Current additions done by Hossam A. H. Fahmy with permission from Michael J. Flynn

Starting material based partly on the book:

Introduction to Arithmetic for Digital Systems Designers

by Shlomo Waser and Michael J. Flynn

Originally published by Holt, Rinehard & Winston,

New York, 1982 (Out of print)

# Contents

| 1 | Nu  | meric Data   | a Representation                               | 1  |

|---|-----|--------------|------------------------------------------------|----|

|   | 1.1 | Infinite asp | pirations and finite resources                 | 2  |

|   | 1.2 | Natural N    | umbers, Finitude, and Modular Arithmetic       | 3  |

|   |     | 1.2.1 Pro    | operties                                       | 4  |

|   |     | 1.2.2 Ext    | tending Peano's Numbers                        | 6  |

|   | 1.3 | Integer Re   | presentation                                   | 7  |

|   |     | 1.3.1 Con    | mplement Coding                                | 8  |

|   |     | 1.3.2 Rac    | dix Complement Code—Subtraction Using Addition | 9  |

|   |     | 1.3.3 Dir    | ninished Radix Complement Code                 | 10 |

|   | 1.4 | Implement    | ation of Integer Operations                    | 15 |

|   |     | 1.4.1 Neg    | gation                                         | 15 |

|   |     | 1.4.2 Tw     | ro's Complement Addition                       | 15 |

|   |     | 1.4.3 On     | es Complement Addition                         | 16 |

|   |     | 1.4.4 Con    | mputing Through the Overflows                  | 17 |

|   |     | 1.4.5 Ari    | thmetic Shifts                                 | 18 |

|   |     | 1.4.6 Mu     | ltiplication                                   | 19 |

|   |     | 1.4.7 Div    | vision                                         | 20 |

|   | 1.5 | Going far    | and beyond                                     | 21 |

|   |     | 1.5.1 Fra    | ections                                        | 21 |

|   |     | 1.5.2 Is t   | the radix a natural number?                    | 22 |

|   |     | 1.5.3 Rec    | dundant representations                        | 23 |

|   |     | 1.5.4 Mix    | xed radix systems                              | 25 |

iv CONTENTS

|   | 1.6 | Further readings                                         |    |  |  |  |  |  |  |

|---|-----|----------------------------------------------------------|----|--|--|--|--|--|--|

|   | 1.7 | Summary                                                  | 28 |  |  |  |  |  |  |

|   | 1.8 | Problems                                                 | 29 |  |  |  |  |  |  |

| 2 | Are | there any limits?                                        | 35 |  |  |  |  |  |  |

|   | 2.1 | The logic level and the technology level                 | 36 |  |  |  |  |  |  |

|   | 2.2 | The Residue Number System                                | 38 |  |  |  |  |  |  |

|   |     | 2.2.1 Representation                                     | 38 |  |  |  |  |  |  |

|   |     | 2.2.2 Operations in the Residue Number System            | 39 |  |  |  |  |  |  |

|   |     | 2.2.3 Selection of the Moduli                            | 41 |  |  |  |  |  |  |

|   |     | 2.2.4 Operations with General Moduli                     | 42 |  |  |  |  |  |  |

|   |     | 2.2.5 Conversion To and From Residue Representation      | 43 |  |  |  |  |  |  |

|   |     | 2.2.6 Uses of the Residue Number System                  | 47 |  |  |  |  |  |  |

|   | 2.3 | The limits of fast arithmetic                            | 48 |  |  |  |  |  |  |

|   |     | 2.3.1 Background                                         | 48 |  |  |  |  |  |  |

|   |     | 2.3.2 Levels of evaluation                               | 48 |  |  |  |  |  |  |

|   |     | 2.3.3 The $(r,d)$ Circuit Model                          | 49 |  |  |  |  |  |  |

|   |     | 2.3.4 First Approximation to the Lower Bound             | 51 |  |  |  |  |  |  |

|   |     | 2.3.5 Spira/Winograd bound applied to residue arithmetic | 53 |  |  |  |  |  |  |

|   |     | 2.3.6 Winograd's Lower Bound on Multiplication           | 54 |  |  |  |  |  |  |

|   | 2.4 | Modeling the speed of memories                           | 56 |  |  |  |  |  |  |

|   | 2.5 | Modeling the multiplexers and shifters                   | 58 |  |  |  |  |  |  |

|   | 2.6 | Additional Readings                                      | 60 |  |  |  |  |  |  |

|   | 2.7 | Summary                                                  | 61 |  |  |  |  |  |  |

|   | 2.8 | Problems                                                 | 62 |  |  |  |  |  |  |

| 3 | Ada | lition and Subtraction (Incomplete chapter)              | 65 |  |  |  |  |  |  |

|   | 3.1 | Fixed Point Algorithms                                   | 65 |  |  |  |  |  |  |

|   |     | 3.1.1 Historical Review                                  | 65 |  |  |  |  |  |  |

|   |     | 3.1.2 Conditional Sum                                    | 66 |  |  |  |  |  |  |

|   |     | 3.1.3 Carry-Look-Ahead Addition                          | 70 |  |  |  |  |  |  |

CONTENTS

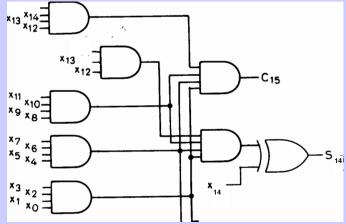

|   |      | 3.1.4   | Canonic Addition: Very Fast Addition and Incrementation          | 74  |

|---|------|---------|------------------------------------------------------------------|-----|

|   |      | 3.1.5   | Ling Adders                                                      | 81  |

|   |      | 3.1.6   | Simultaneous Addition of Multiple Operands: Carry-Save Adders    | 85  |

|   | 3.2  | Proble  | ems                                                              | 87  |

| 4 | Go   | forth   | and multiply (Incomplete chapter)                                | 91  |

|   | 4.1  | Simpl   | e multiplication methods                                         | 91  |

|   | 4.2  | Simul   | taneous Matrix Generation and Reduction                          | 96  |

|   |      | 4.2.1   | Partial Products Generation: Booth's Algorithm                   | 98  |

|   |      | 4.2.2   | Using ROMs to Generate Partial Products                          | .01 |

|   |      | 4.2.3   | Partial Products Reduction                                       | .04 |

|   | 4.3  | Iterat  | ion and Partial Products Reduction                               | .07 |

|   |      | 4.3.1   | A Tale of Three Trees                                            | 07  |

|   | 4.4  | Iterat  | ive Array of Cells                                               | 14  |

|   | 4.5  | Detail  | ed Design of Large Multipliers                                   | 18  |

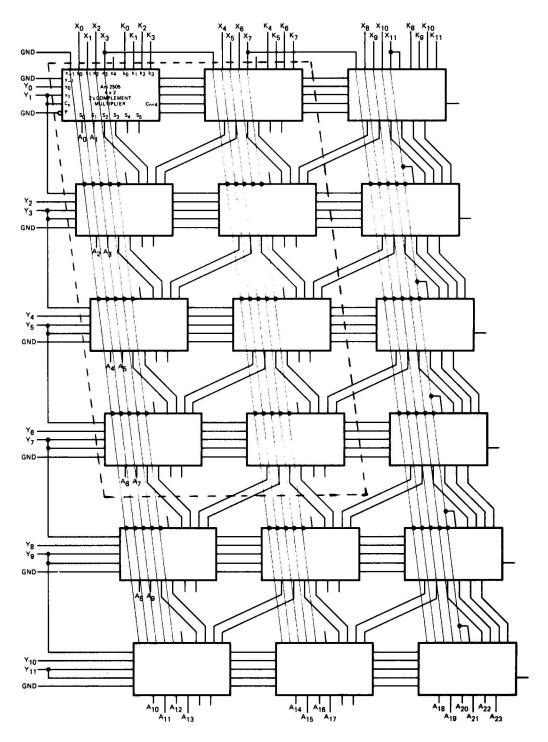

|   |      | 4.5.1   | Design Details of a $64 \times 64$ Multiplier                    | 18  |

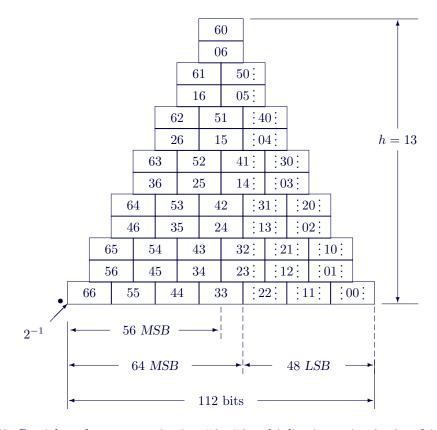

|   |      | 4.5.2   | Design Details of a $56 \times 56$ Single Length Multiplier      | 23  |

|   | 4.6  | Proble  | ems                                                              | .27 |

| 5 | Floa | ating o | over the vast seas 1                                             | 35  |

|   | 5.1  | Motiv   | ation and Terminology; or the why? and what? of floating point 1 | 135 |

|   | 5.2  | Prope   | rties of Floating Point Representation                           | .37 |

|   |      | 5.2.1   | Lack of Unique Representation                                    | .37 |

|   |      | 5.2.2   | Range and Precision                                              | .39 |

|   |      | 5.2.3   | Mapping Errors: Overflows, Underflows, and Gap                   | .40 |

|   | 5.3  | Proble  | ems in Floating Point Computations                               | 41  |

|   |      | 5.3.1   | Representational error analysis and radix tradeoffs              | 41  |

|   |      | 5.3.2   | Loss of Significance                                             | .46 |

|   |      | 5.3.3   | Rounding: Mapping the Reals into the Floating Point Numbers 1    | 48  |

|   | 5.4  | Histor  | ry of floating point standards                                   | .50 |

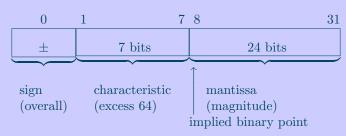

|   |      | 5.4.1   | IEEE binary formats                                              | .52 |

vi CONTENTS

|   |      | 5.4.2   | Prior formats                              |

|---|------|---------|--------------------------------------------|

|   |      | 5.4.3   | Comparing the different systems            |

|   |      | 5.4.4   | Who needs decimal and why?                 |

|   |      | 5.4.5   | IEEE decimal formats                       |

|   | 5.5  | Floati  | ng Point Operations                        |

|   |      | 5.5.1   | Addition and Subtraction                   |

|   |      | 5.5.2   | Multiplication                             |

|   |      | 5.5.3   | Division                                   |

|   |      | 5.5.4   | Fused Multiply Add                         |

|   | 5.6  | Readin  | ng the fine print in the standard          |

|   |      | 5.6.1   | Rounding                                   |

|   |      | 5.6.2   | Exceptions and What to Do in Each Case     |

|   |      | 5.6.3   | Analysis of the IEEE 754 standard          |

|   | 5.7  | Cray I  | Floating Point                             |

|   |      | 5.7.1   | Data Format                                |

|   |      | 5.7.2   | Machine Maximum                            |

|   |      | 5.7.3   | Machine Minimum                            |

|   |      | 5.7.4   | Treatment of Zero                          |

|   |      | 5.7.5   | Operations                                 |

|   |      | 5.7.6   | Overflow                                   |

|   | 5.8  | Additi  | onal Readings                              |

|   | 5.9  | Summ    | ary                                        |

|   | 5.10 | Proble  | ems                                        |

| 3 | Divi | ision ( | Incomplete chapter) 193                    |

|   | 6.1  | Subtra  | active Algorithms: General Discussion      |

|   |      | 6.1.1   | Restoring and Nonrestoring Binary Division |

|   |      | 6.1.2   | Pencil and Paper Division                  |

|   | 6.2  | Multip  | plicative Algorithms                       |

|   |      | 6.2.1   | Division by Series Expansion               |

|   |      | 6.2.2   | The Newton–Raphson Division                |

|   | 6.3  | Additi  | onal Readings                              |

|   | 6.4  |         | ems                                        |

| CONTENTS               | vii |  |

|------------------------|-----|--|

| Solutions              | 207 |  |

| Solutions to Exercises | 208 |  |

| Bibliography           | 229 |  |

| Index                  | 235 |  |

viii CONTENTS

# List of Figures

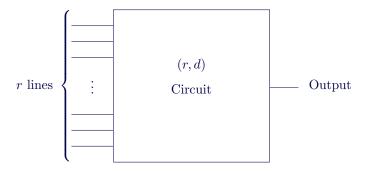

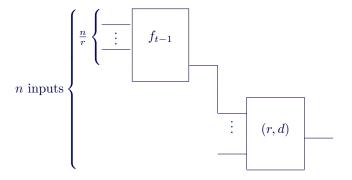

| 2.1 | The $(r,d)$ circuit                                                                                                                                                                                                                                      | 50  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

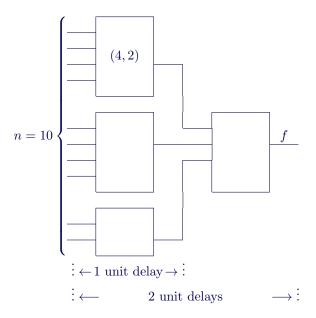

| 2.2 | Time delays in a circuit with 10 inputs and $(r,d)=(4,2)$                                                                                                                                                                                                | 52  |

| 2.3 | The $(r,d)$ network                                                                                                                                                                                                                                      | 53  |

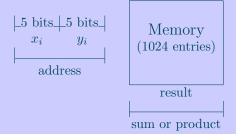

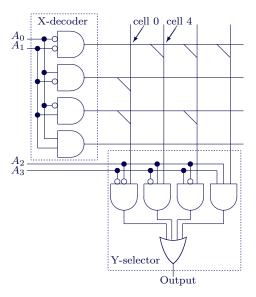

| 2.4 | A simple memory model                                                                                                                                                                                                                                    | 57  |

| 3.1 | Example of the conditional sum mechanism                                                                                                                                                                                                                 | 67  |

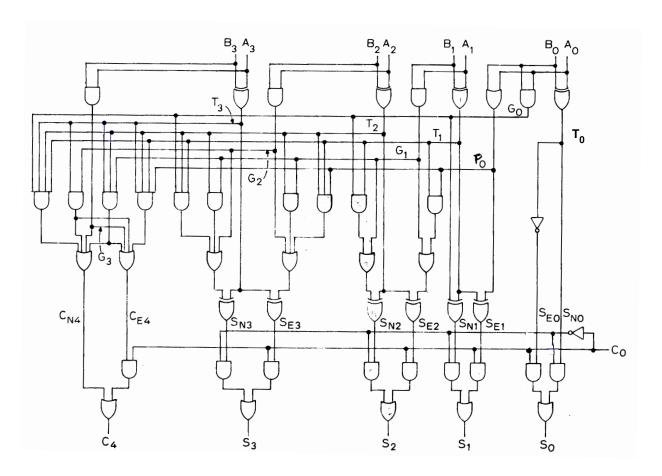

| 3.2 | 4-bit conditional sum adder slice with carry-look-ahead (gate count= 45)                                                                                                                                                                                 | 69  |

| 3.3 | 16-bit conditional sum adder. The dotted line encloses a 4-bit slice with internal look ahead. The rectangular box (on the bottom) accepts conditional carries and generates fast true carries between slices. The worst case path delay is seven gates. | 70  |

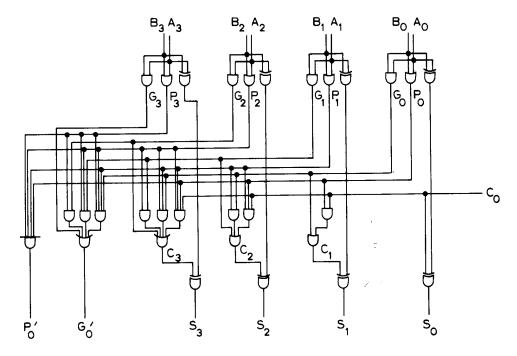

| 3.4 | 4-bit adder slice with internal carry-look-ahead (gate count $=30$ )                                                                                                                                                                                     | 72  |

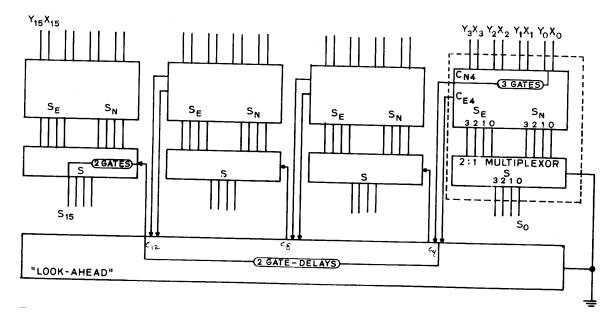

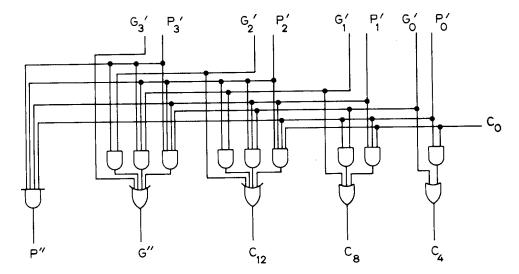

| 3.5 | Four group carry-look-ahead generator (gate count = 14)                                                                                                                                                                                                  | 73  |

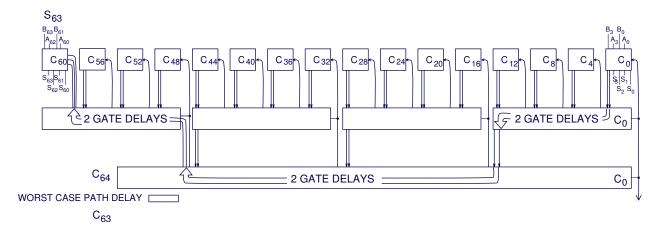

| 3.6 | 64-bit addition using full carry-look-ahead.                                                                                                                                                                                                             | 74  |

| 3.7 | Addition of three <i>n</i> -bit numbers                                                                                                                                                                                                                  | 85  |

| 3.8 | Addition of four <i>n</i> -bit numbers                                                                                                                                                                                                                   | 86  |

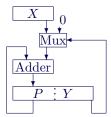

| 4.1 | A simple implementation of the add and shift multiplication                                                                                                                                                                                              | 94  |

| 4.2 | A variation of the add and shift multiplication                                                                                                                                                                                                          | 94  |

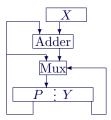

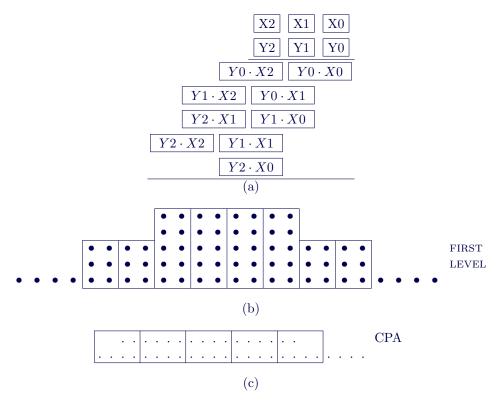

| 4.3 | Multiplying two 8-bit operands                                                                                                                                                                                                                           | 97  |

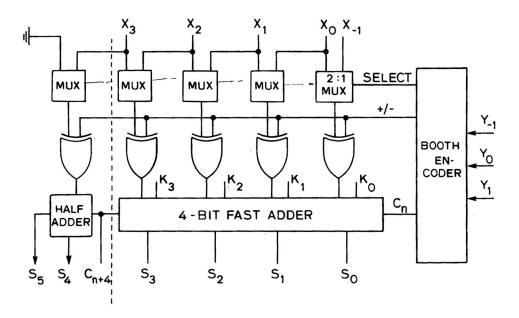

| 4.4 | Generation of five partial products in $8 \times 8$ multiplication, using modified Booth's algorithm (only four partial products are generated if the representation is restricted to two's complement).                                                 | 100 |

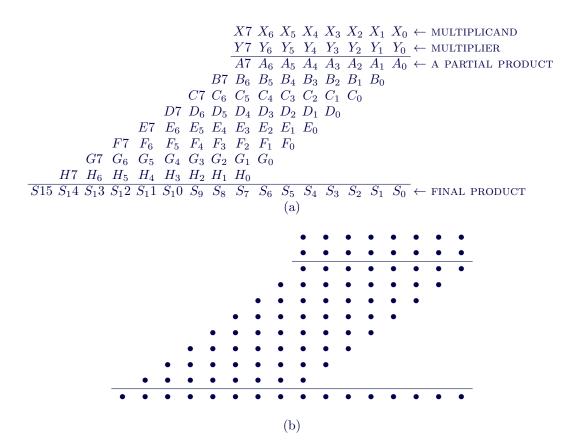

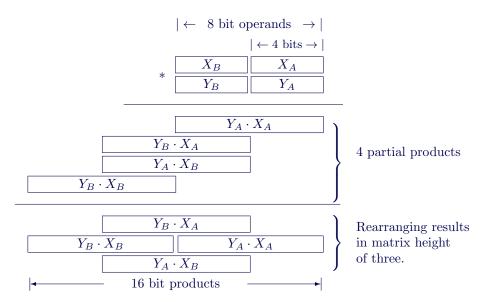

| 4.5 | Implementation of $8 \times 8$ multiplication using four $256 \times 8$ ROMs, where each ROM performs $4 \times 4$ multiplication                                                                                                                        | 102 |

| 4.6 | Using ROMs for various multiplier arrays                                                                                                                                                                                                                 | 103 |

x LIST OF FIGURES

| 4.7 Wallace tree                                                                                                                                     | . 105      |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.8 Wallace tree reduction of $8\times 8$ multiplication, using carry save adders (CSA)                                                              | . 106      |

| 4.9 The $(5,5,4)$ reduces the five input operands to one operand                                                                                     | . 107      |

| 4.10 Some generalized counters from Stenzel Stenzel $et~al.~[1977].$                                                                                 | . 108      |

| 4.11 $12 \times 12$ bit partial reduction using $(5,5,4)$ counters                                                                                   | . 109      |

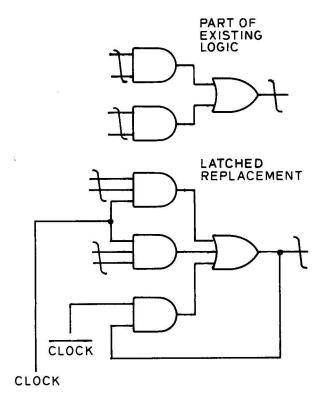

| 4.12 Earle latch                                                                                                                                     | . 110      |

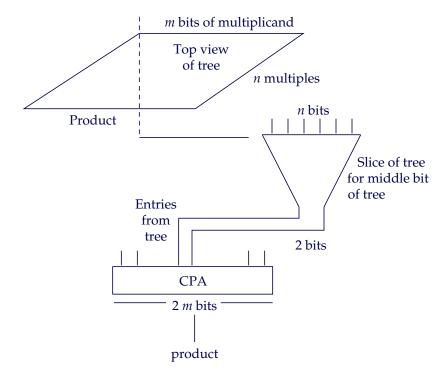

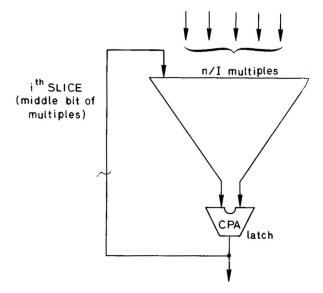

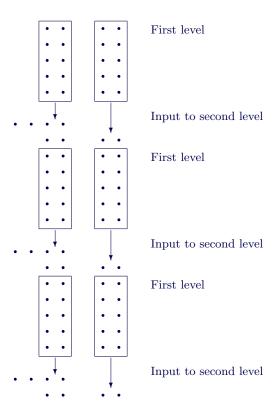

| 4.13 Slice of a simple iteration tree showing one product bit                                                                                        | . 111      |

| 4.14 Slice of tree iteration showing one product bit                                                                                                 | . 112      |

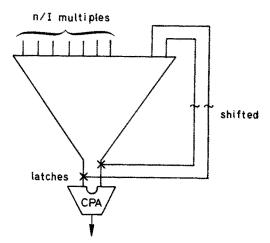

| 4.15 Slice of low level tree iteration                                                                                                               | . 113      |

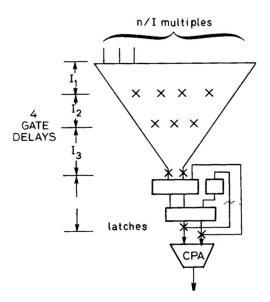

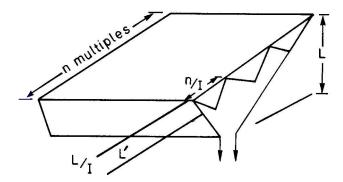

| 4.16 Iteration                                                                                                                                       | . 114      |

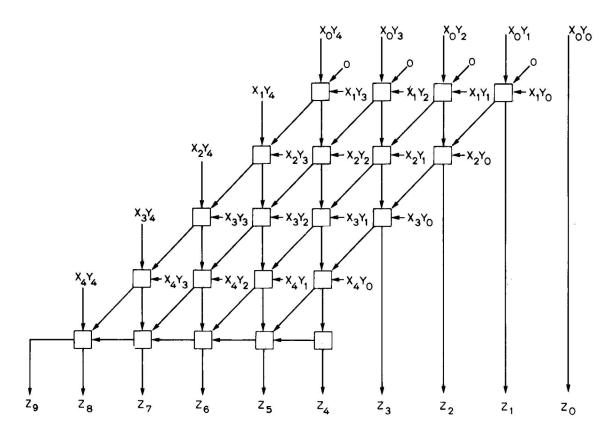

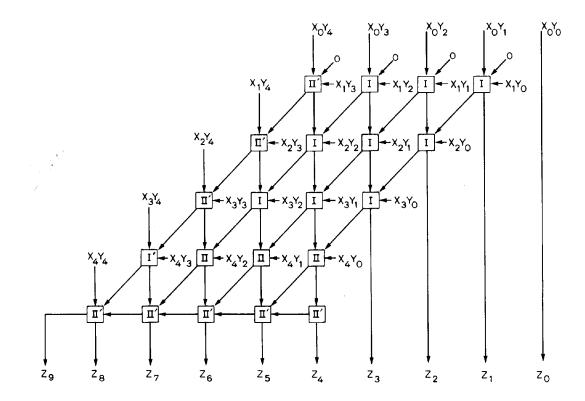

| 4.17 $5 \times 5$ unsigned multiplication                                                                                                            | . 116      |

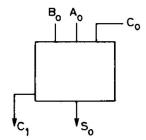

| 4.18 1-bit adder cell                                                                                                                                | . 116      |

| 4.19 $5 \times 5$ two's complement multiplication [PEZ 70]                                                                                           | . 117      |

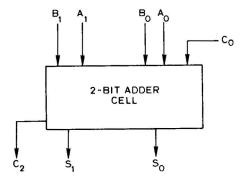

| 4.20 2-bit adder cell                                                                                                                                | . 118      |

| 4.21 Block diagram of $2 \times 4$ iterative multiplier                                                                                              | . 119      |

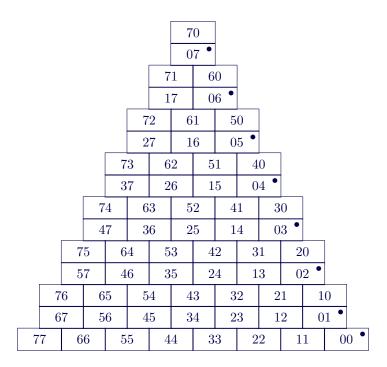

| 4.22 $12 \times 12$ two's complement multiplication $A = X \cdot Y + K$ . Adapted from [Ghest 1971]                                                  |            |

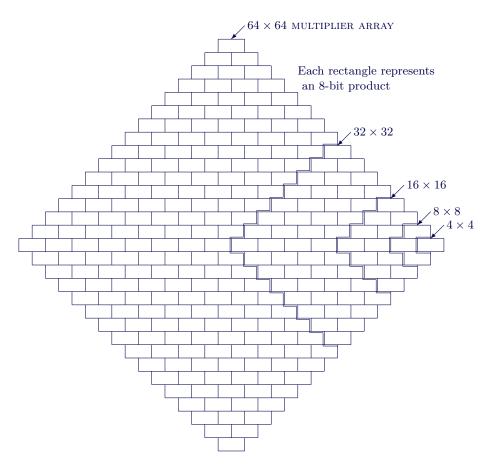

| 4.23 A $64 \times 64$ multiplier using $8 \times 8$ multipliers                                                                                      | . 121      |

| 4.24 Partial products generation of $64 \times 64$ multiplication                                                                                    | . 121      |

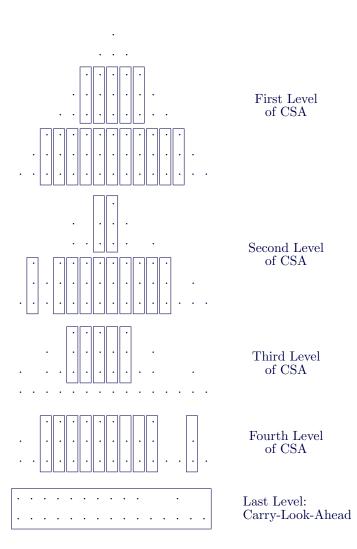

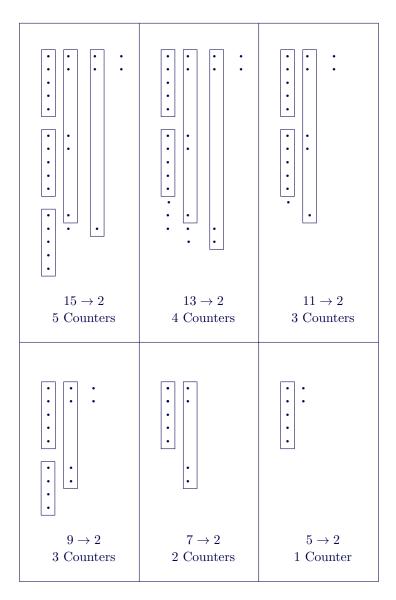

| 4.25 Using $(5,5,4)$ s to reduce various column heights                                                                                              | . 122      |

| 4.26 Reduction of the partial products of height 15                                                                                                  | . 124      |

| 4.27 Partial products generation in a $56 \times 56$ multiplication                                                                                  | . 125      |

| 4.28 Building blocks for problem 4.22                                                                                                                | . 131      |

|                                                                                                                                                      | 150        |

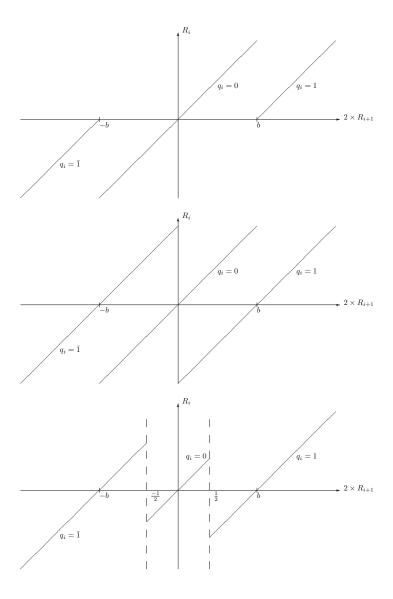

| 5.1 Rounding methods on the real number axis                                                                                                         |            |

| 5.2 IEEE IEEE single (binary32), double (binary64), and quad (binary128) floating point number formats                                               |            |

| 5.3 IEEE decimal64 and decimal128 floating point formats                                                                                             | . 159      |

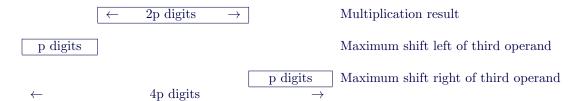

| 5.4 Alignment shift for the FMA                                                                                                                      | . 164      |

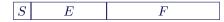

| 6.1 Partial remainder computations in restoring and nonrestoring division                                                                            | . 196      |

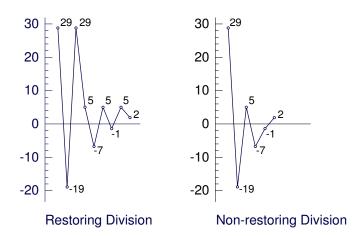

| 6.2 Plot of the curve $f(X) = 0.75 - \frac{1}{X}$ and its tangent at $f(X_1)$ , where $X_1 = 1$ (first guess). $f'(x_1) = \frac{\delta y}{\delta x}$ | t<br>. 200 |

# List of Tables

| 1.1 | Some binary coding schemes                                                                                                                   |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2 | A 4 bits negabinary system                                                                                                                   |

| 1.3 | Some decimal coding schemes                                                                                                                  |

| 2.1 | A Partial List of Moduli and Their Prime Factors                                                                                             |

| 2.2 | Time delay of various components in terms of number of $FO_4$ delays. $r$ is the maximum fan-in of a gate and $n$ is the number of inputs 60 |

| 3.1 | Addition speed of hardware realizations and lower bounds                                                                                     |

| 4.1 | Encoding 2 multiplier bits by inspecting 3 bits, in the modified Booth's algorithm. 99                                                       |

| 4.2 | Extension of the modified Booth's algorithm                                                                                                  |

| 4.3 | Summary of maximum height of the partial products matrix for the various partial generation schemes where $n$ is the multiple size           |

| 5.1 | Tarde-off between radix and representational errors                                                                                          |

| 5.2 | Maximum and minimum exponents in the binary IEEE IEEE formats                                                                                |

| 5.3 | Encodings of the special values and their meanings                                                                                           |

| 5.4 | Comparison of floating point specification for three popular computers 154                                                                   |

| 5.5 | IEEE IEEE and DEC decoding of the reserved operands                                                                                          |

| 5.6 | Underflow/overflow designations in Cray machines                                                                                             |

xii LIST OF TABLES

# Chapter 1

# Numeric Data Representation

Arithmetic is the science of handling numbers and operating on them. This book is about the arithmetic done on computers. To fulfill its purpose, there is a need to describe the computer representations of the different numbers that humans use and the implementation of the basic mathematical operations such as addition, subtraction, multiplication and division. These operations can be implemented in software or in hardware. The focus of this volume is to introduce the hardware aspects of computer arithmetic. We sprinkled the text freely with examples of different levels of complexity as well as exercises. The exercises are there to be attempted before turning to the solutions at the end of the book. The solutions often expand the concepts further but will not benefit much unless you try to work through the exercises first. At the end of each chapter, there are further problems that are left for the student to solve.

After finishing the book, the reader should be familiar with the fundamentals of the field and able to design simple logic circuits to perform the basic operations. The text often refers to further readings for advanced material. We believe that such a presentation helps introduce new designers to the advanced parts of the field. This presentation style also does not get into too many details and gives a general background for those in other specialities such as computer architecture, VLSI design, and numerical analysis who might be interested to strengthen their knowledge of computer arithemtic.

In fact, if one contemplates the design of large digital integrated circuits one finds that it is mostly composed of four main entities:

**Memories** are used for temporary storage of results (registers), for reducing the time delay of retrieving the information (caches), or as the main store of information (main memories).

Control logic blocks handle the flow of information and assure that the circuit performs what is desired by the user.

**Datapath blocks** are the real engine that performs the work. These are mainly circuits performing either some arithmetic or logic operation on the data.

Communications between all the elements is via wires usually arranged in the form of buses.

In our following discussions, we mainly focus on the datapath and see how it interacts with the three other elements present in digital circuits.

A good optimization of the arithmetic blocks results in an improved datapath which directly leads to a better overall design. Such an optimization might be to improve the speed of operation, to lower the power consumption, to lower the cost of the circuit (usually related to the number of gates used or the area on the chip), or to improve any other desired factor. As the different possibilities for implementing the arithmetic operations are explained, we will see that the designer has a large array of techniques to use in order to fulfill the desired outcome. A skilled designer chooses the best technique for the problem at hand. We hope to help future designers make these informed choices by presenting some simple tools to measure the different factors for the options that they evaluate.

## 1.1 Infinite aspirations and finite resources

Using computers to perform arithemtic introduces some constraints to what can be done. The main one is the limit on the number of digits used. This limitation translates into the representation of only a finite set of numbers. All other numbers from the set of real numbers are not representable. Some of the effects of this finitude are clear. Definitely any irrational number with an infinite number of digits after the fractional point is not representable. The same case applies for rational numbers whose representation as a fractional number is beyond the number of digits available. For example, if we assume a decimal number system with five digits after the fractional point then the number 1234567/500000 = 2.469134 is not represented exactly. Increasing the number of digits used to six may help to include an accurate representation for that rational number, however, the numbers 1/7,  $\sqrt{2}$ , e and  $\pi$  are still not represented.

This finitude also means that there is an upper bound on the numbers that are representable. If an arithmetic operation has a result beyond this upper limit a condition called overflow occurs and either the hardware or the software running on top of it must handle the situation differently to get a meaningful result. Similarly, a lower bound on the minimum absolute value of a fraction exist and a condition called underflow occurs if an arithmetic operation has a result below this limit.

Said differently, the primary problem in computer arithmetic is the mapping from the infinite number systems of mathematics to the finite representational capability of the machine. Finitude is the principal characteristic of a computer number system. Almost all other considerations are a direct consequence of this finitude.

The common solution to this problem is the use of modular arithmetic. In this scheme, every integer from the infinite number set has one unique representation in a finite system. However, now a problem of multiple interpretations is introduced—that is, in a modulo 8 system, the number 9 is mapped into the number 1. As a result of mapping, the number 1 corresponds in the infinite number system to 1,9,17,25, etc.

As humans originally used numbers to count, we start by the natural numbers representing positive integers and see the effect of finitude and modular arithmetic on such numbers. General integer numbers including the representation of negative numbers follow. The presentation of the basic arithmetic operations on integers is given next. Once these fundamentals are laid out,

we refer to further readings that is related. The following chapter deals with the representations of real numbers and the operations involving them.

### 1.2 Natural Numbers, Finitude, and Modular Arithmetic

The historical need for numbers and their first use was for counting. Even nowadays, the child's numerical development starts with counting. The counting function is accomplished by the infinite set of numbers  $1, 2, 3, 4, \ldots$ , which are described as natural numbers. These numbers have been used for thousands of years, and yet only in the  $19^{th}$  century were they described precisely by Peano (1858–1932). The following description of Peano's postulates is adapted from Parker [Parker, 1966].

**Postulate 1:** For every natural number x, there is a unique natural number which we call the successor of x and which is denoted by s(x).

Postulate 2: There is a unique natural number which we call 1.

Postulate 3: The natural number 1 is not the successor of any natural number.

**Postulate 4:** If two natural numbers x and y are such that s(x) = s(y), then x = y.

**Postulate 5:** (Principle of Mathematical Induction): Let  $\mathcal{M}$  be a subset of the natural numbers with the following properties:

- (a) 1 is a member of  $\mathcal{M}$ ;

- (b) For any x that belongs to  $\mathcal{M}$ , s(x) also belongs to  $\mathcal{M}$ .

Then  $\mathcal{M}$  is the set of natural numbers.

Later on, we will show that all other number systems (negative, real, rational) can be described in terms of natural numbers. At this point, our attention is on the problem of mapping from the infinite set to a finite set of numbers.

Garner [Garner, 1965] show that the most important characteristic of machine number systems is finitude. Overflows, underflows, scaling, and complement coding are consequences of this finitude.

On a computer, the infinite set of natural numbers needs to be represented by a finite set of numbers. Arithmetic that takes place within a closed set of numbers is known as *modular arithmetic*. Brennan [Brennan, 1968] provides the following examples of modular arithmetic in everyday life. The clock tells time in terms of the closed set (modules) of 12 hours, and the days of the week all fall within modulo 7. If the sum of any two numbers within such a modulus exceeds the modulus, only the remainder number is considered; e.g., eight hours after seven o'clock, the time is three o'clock, since

$$(8+7)$$

modulo  $12 = \text{remainder of } \frac{15}{12} = 3.$

Seventeen days after Tuesday, the third day of the week, the day is Friday, the sixth day of the week, since

$$(17+3)$$

modulo  $7 = \text{remainder of } \frac{20}{7} = 6.$

In modular arithmetic, the property of congruence (having the same remainder) is of particular importance. By definition [Steinard and Munro, 1971]:

If  $\mu$  is a positive integer, then any two integers N and M are *congruent*, modulo  $\mu$ , if and only if there exists an integer K such that

$$N - M = K\mu.$$

Hence,

$$N\mathbf{mod}_{\mu} \equiv M\mathbf{mod}_{\mu},$$

where  $\mu$  is called the modulus.

Informally, the modulus is the quantity of numbers within which a computation takes place, i.e.  $(0, 1, 2, 3, \dots, \mu - 1.)$

**Example 1.1** If  $\mu = 256$ , M = 258, and N = 514 are M and N congruent  $\mathbf{mod}_{\mu}$ ? *Solution:* The modulo operation yields

$$514 \text{mod}_{256} = 2 \text{mod}_{256}$$

and

$$258 \text{mod}_{256} = 2 \text{mod}_{256},$$

i.e., they are congruent mod<sub>256</sub>, and

$$514 - 258 = 1 \times 256,$$

i.e., K = 1.

#### 1.2.1 Properties

Congruence has the same properties with respect to the operations of addition, subtraction, and multiplication, or any combination.

If

$$N' = N \mathbf{mod}_{\mu}$$

and  $M' = M \mathbf{mod}_{\mu}$ , then

$$(N+M) \mathbf{mod}_{\mu} = (N'+M') \mathbf{mod}_{\mu}$$

$(N-M) \mathbf{mod}_{\mu} = (N'-M') \mathbf{mod}_{\mu}$

$(N \times M) \mathbf{mod}_{\mu} = (N' \times M') \mathbf{mod}_{\mu}$

**Example 1.2** If  $\mu = 4$ , N = 11 and M = 5 check the three operations. *Solution:* Since (11)**mod**<sub>4</sub> = 3 and (5)**mod**<sub>4</sub> = 1, we get

$$(3+1)$$

mod<sub>4</sub> =  $(11+5)$ mod<sub>4</sub>  $\equiv 0$ ,

$(3-1)$ mod<sub>4</sub> =  $(11-5)$ mod<sub>4</sub>  $\equiv 2$ , and

$(3\times1)$ mod<sub>4</sub> =  $(11\times5)$ mod<sub>4</sub>  $\equiv 3$ .

Exercise 1.1 Can you prove that if  $N' = N \mathbf{mod}_{\mu}$  and  $M' = M \mathbf{mod}_{\mu}$ , then  $(N[+,-,\times]M)\mathbf{mod}_{\mu} = (N'[+,-,\times]M')\mathbf{mod}_{\mu}$  where  $[+,-,\times]$  means any of the addition, subtraction, or multiplication operations?

Negative numbers pose a small difficulty. If N is negative while  $\mu$  is positive in the operation  $N\mathbf{mod}_{\mu}$  then several conventions apply. Depending on how it is defined,

$$-7$$

**mod**<sub>3</sub>  $\equiv -1$  or  $+2$ ,

since

$$\frac{-7}{3} = -2$$

quotient,  $-1$  remainder

or

$$\frac{-7}{3} = -3$$

quotient,  $+2$  remainder.

For modulus operations, the usual convention is to choose the *least positive residue* (including zero). Unless otherwise specified, we will assume this convention throughout this book, even if we are dividing by a negative number such as (-7)/(-3) = +2. That is,

$$\frac{-7}{-3} = +3$$

quotient,  $+2$  remainder.

In terms of conventional division, this is surprising, since one might expect

$$\frac{-7}{-3} = +2$$

quotient,  $-1$  remainder.

We will distinguish between the two division conventions by referring to the former as *modulus division* and the latter as *signed division*. In signed division, the magnitude of the quotient is independent of the signs of the divisor and dividend. This distinction follows the work of Warren and his colleagues [Warren et al., 1979].

- Exercise 1.2 For the operation of integer division  $\pm 11 \div \pm 5$  find the quotient and remainder for each of the four sign combinations

- (a) for signed division, and

- (b) for modulus division.

The division operation is defined as

$$\frac{a}{b} = q + \frac{r}{b},$$

where q is the quotient and r is the remainder. But even the modulus division operation does not extend as simply as the other three operations; for example,

$$\frac{3}{1} \neq \frac{11}{5} \mathbf{mod_4}.$$

Nevertheless, division is a central operation in modular arithmetic. It can be shown that for any modulus division  $M/\mu$ , there is a unique quotient-remainder pair, and the remainder has one of the  $\mu$  possible values  $0, 1, 2, \ldots, \mu - 1$  which leads to the concept of residue class.

A residue class is the set of all integers having the same remainder upon division by the modulus  $\mu$ . For example, if  $\mu=4$ , then the numbers 1, 5, 9, 13 . . . are of the same residue class. Obviously, there are exactly  $\mu$  residue classes, and each integer belongs to one and only one residue class. Thus, the modulus  $\mu$  partitions the set of all integers into  $\mu$  distinct and disjoint subsets called residue classes.

**Example 1.3** If  $\mu = 4$ , find the residue classes. Solution: In this case, there are four residue classes which partition the integers:

$$\begin{cases} \dots, & -8, & -4, & 0, & 4, & 8, & 12, & \dots \\ \dots, & -7, & -3, & 1, & 5, & 9, & 13, & \dots \\ \dots, & -6, & -2, & 2, & 6, & 10, & 14, & \dots \\ \dots, & -5, & -1, & 3, & 7, & 11, & 15, & \dots \end{cases}$$

If we are not dealing with individual integers but only with the residue class of which the integer is a member, the problem of working with an infinite set is reduced to one of working with a finite set. This is a basic principle of number representation in computers.

Before we leave these points, let us check that you understand them thoroughly.

- Exercise 1.3 If  $\div_m$  denotes the modular division so that  $N \div_m D$  result in  $q_m$  and  $r_m$  as the quotient and remainder while  $\div_s$  (with  $q_s$ ,  $r_s$ ) denotes signed division, find  $q_s$  and  $r_s$  in terms of  $q_m$  and  $r_m$ .

- Exercise 1.4 Another type of division is possible; this is called "floor division." In this operation, the quotient is the greatest integer that is contained by (is less than or equal to) the numerator divided by the denominator (note that minus 3 is greater than minus 4). Find  $q_f$ ,  $r_f$  in terms of  $q_m$ ,  $r_m$ .

#### 1.2.2 Extending Peano's Numbers

Peano's numbers are the natural integers 1, 2, 3, ..., but in real life we deal with more numbers. The historic motivation for the extension can be understood by studying some arithmetic operations. The operations of addition and multiplication (on Peano's numbers) result in numbers that are still described by the original Peano's postulates. However, subtraction of two numbers may result in negative numbers or zero. Thus, the extended set of all integers is

$$-\infty, \ldots, -2, -1, 0, 1, 2, \ldots + \infty,$$

and natural integers are a subset of these integers. The operation of division on integers may result in noninteger numbers. By definition, such a number is a rational number, which is represented exactly as a ratio of two integers. However, if the rational number is to be approximated as a single number, an infinite sequence of digits may be required for such a number, for example, 1/3 = 0.33333... Between any two rational numbers, however small but finite their difference, lies an infinite number of other rational numbers and infinitely more numbers which cannot be expressed as rationals. We call these latter numbers real numbers and they include such constants as  $\pi$  and e. Real numbers can be viewed as all points along the number axis from  $-\infty$  to  $+\infty$ .

Real numbers need to be represented in a machine with the characteristics of finitude. This is accomplished by approximating real numbers and rational numbers by terminating sequences of digits. Thus, all numbers (real, rational, and integers) can be operated on as if they were integers (provided scaling and rounding are done properly). We devote the remainder of this chapter to integers. Other numbers are discussed in subsequent chapters.

## 1.3 Integer Representation

The data representation to be described here is a weighted positional representation. The development for a weighted system was a particular breakthrough in ancient man's way of counting. While his hearthmate was simmering clams, and children demanding equal portions, to count seventeen shells he may have counted the first ten and marked something in the sand (to indicate 10), then counted the remaining seven shells. If his mark on the sand happened to look like 1, he could easily have generated the familiar (decimal) weighted positional number system.

The decimal system is also called base-10 system and its digits range from 0 to 9, i.e. from 0 to 10-1. For the decimal system, 10 is called the radix and the digits usually go up to the radix minus one. The same idea applies for other systems. For example, in a binary (base-2) system the digits usually are 0 or 1, in a base-8 system the digits are usually 0 to 7. A number N with n digits  $(d_{n-1}, \dots, d_0)$  in the radix  $\beta$  is written as  $d_{n-1} d_{n-2} d_{n-3} \dots d_1 d_0$ . The  $d_0$  represents the units or  $\beta^0$  values, the  $d_1$  represents the  $\beta^1$  values, the  $d_2$  represents the  $\beta^2$  values and so on. The total value of N is  $\sum_{i=0}^{i=n-1} d_i \beta^i$ . Such a system is called a weighted positional number system since each position has a weight and the digits are multiplied by that weight. This system was invented in India and developed by the Muslims who called it hisab al-hind pair i which is i in i in i in i is i in i

That Indo-Arabic system was later introduced to Europe through the Islamic civilization in Spain and replaced the Roman numerals. That is the reason why the numerals 0 to 9 are known

in the west as the Arabic numerals. A simple idea links the Roman system to the much older Egyptian system: the units have a symbol used to count them and that symbol is repeated to count for more than one. A group of five units has a different symbol. Ten units have another symbol, fifty units have yet another symbol and so on. This Roman system only survives today for special applications such as numbering the chapters of a book but is not in much use in arithmetic. Another number system that existed in history is the Babylonian system which was a sexadecimal system and it survives today in the way we tell the time by dividing the hour into sixty minutes and the minute into sixty seconds. Chapter 2 discusses the advantages gained from some alternative number systems.

**Example 1.4** In the familiar decimal system, the base is  $\beta = 10$ , and the 4-digit number 1736 is:

$$1736 = 1 \times 10^3 + 7 \times 10^2 + 3 \times 10^1 + 6.$$

In the binary system,  $\beta = 2$ , and the 5-digit number 10010 is:

$$1 \times 2^4 + 0 \times 2^3 + 0 \times 2^2 + 1 \times 2 + 0 = 18$$

(base 10).

The leading digit,  $d_m$ , is the most significant digit (MSD) or the most significant bit (MSB) for binary base. Similarly,  $d_0$  is the least significant digit or bit—(LSD or LSB) respectively.

The preceding positional number system does not include a representation of negative numbers. Two methods are commonly used to represent signed numbers [Garner, 1965]:

**Sign plus magnitude:** Digits are represented according to the simple positional number system; an additional high-order symbol represents the sign. This code is natural for humans, but unnatural for a modular computer system.

Complement codes: Two types are commonly used; namely, radix complement code (RC) and diminished radix complement code (DRC). Complement coding is natural for computers, since no special sign symbology or computation is required. In binary arithmetic (base = 2), the RC code is called two's complement and the DRC is called ones' complement.

#### 1.3.1 Complement Coding

Suppose for a moment that we had a modular number system with modulus  $2\mu$ . We could designate numbers in the range 0 to  $\mu-1$  as positive numbers similar to the case of our previous modulus  $\mu$  system, and *treat* numbers  $\mu$  to  $2\mu-1$  as negative, since they lie in the same residue class as numbers  $-(\mu)$  to -1:

$$\begin{array}{lcl} -1\mathbf{mod_{2\mu}} &=& (2\mu-1)\mathbf{mod_{2\mu}}; \\ -(\mu)\mathbf{mod_{2\mu}} &=& (2\mu-\mu)\mathbf{mod_{2\mu}} = \mu\mathbf{mod_{2\mu}}. \end{array}$$

Mapping these negative numbers into large positive residues is called *complement coding*. We deal with  $2\mu - x$  rather than -x. However, because both representations are congruent, they produce the same modular results.

Of course, "overflows" are a problem. These are results that appear as correct representations  $\mathbf{mod_{2}}_{\mu}$ , but are incorrect in our mapped  $\mathbf{mod}_{\mu}$  system. If two positive or two negative numbers a and b have sum c, which exceeds  $|\mu|$ , overflow occurs and this must be detected. The decision to actually use the **RC** or the **DRC** makes the implementation details differ slightly.

#### 1.3.2 Radix Complement Code—Subtraction Using Addition

We start the discussion by supposing that a number N is a positive integer of the form

$$N = d_m \cdot \beta^m + d_{m-1} \cdot \beta^{m-1} + \dots + d_0.$$

Exercise 1.5 If the digits  $d_i \in \{0, 1, \dots, \beta - 1\}$ , prove that the maximum value N may assume is  $\beta^{m+1} - 1$ .

Now, suppose we wish to represent -N, a negative m+1 digit number. We define the radix complement of N as

$$\mathbf{RC}(N) = \beta^{m+1} - N.$$

Clearly, the RC(N) is a nonnegative integer.

For ease of representation, let us assume that  $\beta$  is even and let n = m+1; then  $\mathbf{RC}(N) = \beta^n - N$ . Suppose P and N are n-digit numbers and we wish to compute P - N using the addition operation. P and N may be either positive or negative numbers, as long as

$$\frac{\beta^n}{2} - 1 \ge P, \ N \ge \frac{-\beta^n}{2}.$$

In fact, P - N is more accurately  $(P - N) \mathbf{mod}_{\beta^n}$ , and

$$(P-N)$$

$\mathbf{mod}_{\beta^{\mathbf{n}}} = (P\mathbf{mod}_{\beta^{\mathbf{n}}} - N\mathbf{mod}_{\beta^{\mathbf{n}}})$  $\mathbf{mod}_{\beta^{\mathbf{n}}}.$

However, if we replace -N with  $\beta^n - N$  the equality is unchanged. That is, by taking

$$(P\mathbf{mod}_{\beta^{\mathbf{n}}} + (\beta^n - N)\mathbf{mod}_{\beta^{\mathbf{n}}}) \mathbf{mod}_{\beta^{\mathbf{n}}},$$

we get

$$P\mathbf{mod}_{\beta^{\mathbf{n}}} - N\mathbf{mod}_{\beta^{\mathbf{n}}}.$$

The computation of  $\beta^n - N$  is relatively straightforward.

- 1. Scan the digits of N from the least significant side till you reach the first non-zero digit. Assume this non-zero digit is at position i+1.

- 2. The digits of RC(N) are given by

$$\mathbf{RC}(N)_{j} = \begin{cases} 0 & 0 \le j \le i \\ \beta - d_{i+1} & j = i+1 \\ \beta - 1 - d_{j} & i+2 \le j \le m \end{cases}$$

i.e., the first non-zero digit is subtracted from  $\beta$  and all the other digits at higher positions are subtracted from  $\beta - 1$ .

For example, in a three-position decimal number system, the radix complement of the positive number 245 is 1000 - 245 = 755. In this system,  $\beta = 10$ , n = 3 and, according to our definition, 755 represents a negative number since  $755 > \beta^n/2$ .

This presentation of radix complement illustrates that by properly scaling the represented positive and negative numbers about zero, no special treatment of the sign is required. In fact, the most significant digit indicates the sign of the number. In the base 10 system, the digits 5, 6, 7, 8, 9 (in the most significant position) indicate negative numbers; i.e., three decimal digits represent numbers from +499 to -500.

**Example 1.5** If P = +250 and N = +245 compute P - N using the radix complement.

Solution:

$$\begin{array}{ccc}

250 & \Rightarrow & 250 \\

-245 & & +755 \\

\hline

& & 1005 & \mathbf{mod_{1000}} \equiv 5

\end{array}$$

Exercise 1.7 In the specific case of the binary system, a most significant digit of 1 is an indication of negative numbers. A nice property follows for the two's complement binary system, If a binary number N is represented in two's complement form by the bit string  $d_m d_{m-1} \cdots d_1 d_0$ , then  $N = (-1)d_m 2^m + \sum_{i=0}^{m-1} d_i 2^i$ . Can you prove it?

For the familiar case of even radix, a disadvantage of the radix complement code is the asymmetry around zero; that is, the number of negative numbers is greater by one than the number of positive numbers. However, this shortcoming is not a serious one. If the number zero is viewed as a positive number then there are as many positive numbers as there are negative numbers!

Although the operation of finding the radix complement is quite simple as shown in exercise 1.6 it is a sequential operation. We scan the digits in sequence and hence it takes time to perform it. The greatest disadvantage of the two's complement number system is this difficulty in converting from positive to negative numbers, and vice versa. This difficulty is the motivation [Stone, 1975] for developing the diminished radix complement code.

#### 1.3.3 Diminished Radix Complement Code

By definition, the diminished radix complement of the previously defined number N,  $\mathbf{DRC}(N)$  is  $\beta^n - 1 - N$ . In a decimal number system, this code is called *nines' complement*, and in binary system, it is called *ones' complement*.

The computation of the diminished radix complement (**DRC**) is simpler than that of the radix complement. Since, if  $N \mathbf{mod}_{\beta^{\mathbf{n}}} = d_{n-1}d_{n-2}\dots d_0$ , then for all  $d_i(n-1 \ge i \ge 0)$

$$\mathbf{DRC}(d)_i = \beta - 1 - d_i.$$

Since  $\beta - 1$  is the highest valued symbol in a radix  $\beta$  system, no borrows can occur and the **DRC** digits can be computed independently.

**Example 1.6** To verify their independence, calculate the digits representing the diminished radix complement of N = +245 starting from the most significant side. *Solution:*

$$9-2 = 7$$

$9-4 = 5$

$9-5 = 4$

DRC(245) = 754

It is easy to verify that doing the digits in any order yields the same result.

This simplicity of the diminished radix complement computation comes at some expense in arithmetic operation as shown in the following example.

**Example 1.7** Suppose we have two  $\mathbf{mod_{99}}$  numbers P and N, i.e. each having two digits. The following operations are performed by allowing a carry to overflow to the third digit position. The operations are thus  $\mathbf{mod_{1000}}$  originally, then we correct the result to  $\mathbf{mod_{100}}$  and finally to  $\mathbf{mod_{99}}$ :

(i)

$$P = 47$$

,  $N = 24$ :

$$\begin{array}{r}

47 \\

+24 \\

\hline

071

\end{array}$$

$$71 \text{mod}_{100} \equiv 71 \text{mod}_{99} = \text{result.}$$

(ii)

$$P = 47$$

,  $N = 57$ :

$$\begin{array}{c|c}

47 \\

+57 \\

\hline

104 \\

+1 \\

\hline

05

\end{array}$$

$$4 \text{mod}_{100} \equiv 5 \text{mod}_{99} = \text{result.}$$

(iii)

$$P = 47$$

,  $N = 52$ :

The  $\mathbf{mod_{99}}$  result is the same as the  $\mathbf{mod_{100}}$  result if the sum is less than 99. If the sum is an exact multiple of 99 the  $\mathbf{mod_{99}}$  result is zero. On the other hand, if the sum exceeds 99 the  $\mathbf{mod_{99}}$  result is greater than the  $\mathbf{mod_{100}}$  result. We add one to the  $\mathbf{mod_{100}}$  result in this latter case.

Basically, if the sum is an exact multiple of 99 the final result is zero, otherwise we add the carry into the third digit position to the **mod**<sub>100</sub> result to get the **mod**<sub>99</sub> result.

To state these findings more formally, since the arithmetic logic itself is always  $\mathbf{mod}_{\beta^{\mathbf{p}}}$ , (where  $p \geq n$ ), we need to define the computation of the sum  $S\mathbf{mod}_{\beta^{\mathbf{n}}-1}$  in terms of  $S\mathbf{mod}_{\beta^{\mathbf{n}}}$ .

Two functions used throughout this book can help. We use the two symbols: [x] and [x],

respectively for the ceiling and the floor of the real number x. The ceiling function is defined as the smallest integer that properly contains x; e.g., if x = 1.33, then  $\lceil x \rceil = \lceil 1.33 \rceil = 2$ . The floor function is defined as the largest integer contained by x, e.g.,  $\lfloor x \rfloor = \lfloor 1.33 \rfloor = 1$ .

If S is initially represented as a  $\mathbf{mod}_{\beta^{\mathbf{p}}}$  number, or the result of addition or subtraction of two numbers  $\mathbf{mod}_{\beta^{\mathbf{n}}}$ , then the conversion to a  $\mathbf{mod}_{\beta^{\mathbf{n}}-1}$  number, S', is

If

$$S < \beta^n - 1$$

then  $S' = S$ .

That is,

$$S\mathbf{mod}_{\beta^{\mathbf{n}}} \equiv S\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} = S'.$$

If  $S = \beta^n - 1$  or in general

$$S = k(\beta^n - 1),$$

where k is any integer, then

$$S' = 0.$$

Finally, if  $\beta^n - 1 < S$ , then S' must be increased by 1 (called the end around carry) for each multiple of  $\beta^n - 1$  contained in S. Thus,

$$S' = \left(S + \lfloor \frac{S}{\beta^n - 1} \rfloor\right) \mathbf{mod}_{\beta^n}.$$

That is, S' is S plus the largest integer contained by  $\frac{S}{\beta^n-1}$ .

Since  $\beta^n - 1$  is a represented element in *n*-digit arithmetic ( $\mathbf{mod}_{\beta^n}$  arithmetic), we have two equivalent representations for zero in the  $\mathbf{mod}_{(\beta^n-1)}$  case:  $\beta^n - 1$  and 0.

The broader issue of  $\beta^n - 1$  and  $\beta^n$  modular compatibility will be of interest to us again in Chapter 2. For the moment, we focus on a restricted version of this issue when using of the **DRC** in subtraction. In order to represent negative numbers using the **DRC**, we will partition the range of  $\beta^n$  representation as follows:

Thus, any m-digit (m = n - 1) number P must be in the following range:

$$\frac{\beta^n}{2} - 1 \ge P \ge \frac{-\beta^n}{2} + 1.$$

Note that  $\frac{\beta^n}{2}$  is congruent to (lies in the same residue class as)  $\frac{-\beta^n}{2} + 1$  modulo  $\beta^n - 1$ , since

$$\left(\frac{-\beta^n}{2}+1\right) \mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} \equiv \left((\beta^n-1)-\frac{\beta^n}{2}+1\right) \mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} \equiv \left(\frac{\beta^n}{2}\right) \mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}}.$$

So long as  $\beta$  has 2 as a factor, there will be a unique set of leading digit identifiers for negative numbers. For example, if  $\beta = 10$ , a negative number will have 5, 6, 7, 8, 9 as a leading digit.

# $\stackrel{?}{\Longrightarrow}$

#### Exercise 1.8 Is it really accurate to say "negative numbers" in the previous paragraph?

Consider the computation P-N using the diminished radix complement (**DRC**) with  $\mathbf{mod}_{\beta^n}$ arithmetic logic to be corrected to  $\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}}$ . P and N satisfy  $\frac{\beta^n}{2}-1\geq P, N\geq \frac{-\beta^n}{2}+1$  and due to the properties of modular arithmetic we have

$$(P-N)\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} \equiv (P\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} - N\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}}) \mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}}.$$

Since  $P\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} = P$  and  $-N\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} = \beta^n - 1 - N$  then

$$(P-N)$$

$\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} = (P+\beta^n-1-N)$  $\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}} \equiv (P+\mathbf{DRC}(N))$  $\mathbf{mod}_{\beta^{\mathbf{n}}-\mathbf{1}}.$

However, the basic addition logic is performed  $\mathbf{mod}_{\beta^n}$ . We must thus correct the  $\mathbf{mod}_{\beta^n}$ difference, S, to find the  $\mathbf{mod}_{\beta^{n}-1}$  difference, S'.

$$S = P + \beta^n - 1 - N.$$

$$\begin{array}{ll} \text{If } S>\beta^n-1\text{, then} & S'=S+1; & \text{i.e., } P-N>0 \text{ .} \\ \text{If } S<\beta^n-1\text{, then} & S'=S; & \text{i.e., } P-N<0 \text{ .} \\ \text{If } S=\beta^n-1\text{, then} & S'=0; & \text{i.e., } P=N \text{ ,} \\ \end{array}$$

If

$$S = \beta^n - 1$$

, then  $S' = 0$ ; i.e.,  $P = N$ ,

and the result is zero (i.e., one of the two representations).

#### Exercise 1.9 If P = +250 and N = +245 compute P - N using the diminished radix complement.

In summary, in the decimal system  $-43 \Rightarrow 99 - 43 = 56$ , and in the binary system  $-3 \Rightarrow$ 111 - 011 = 100. These examples illustrate the advantage of the diminished radix complement code—the ease of initial conversion from positive to negative numbers; the conversion is done by taking the complement of each digit. Of course, in the binary system, the complement is the simple Boolean NOT operation.

A disadvantage of the system is illustrated by taking the complement of zero; for example, in a 3-digit decimal system, the complement of zero = 999 - 000 = 999. Thus, the number zero has two representations: 000 and 999. (Note: the complement of the new zero is 999 - 999 = 000.)

Another disadvantage is that the arithmetic logic may require correction of results (end-around carry)—see Chapter 3.

It is important to remember that the same bit pattern means different things when interpreted differently. Table 1.1 illustrates this fact for all the combinations of four bits and six different coding schemes. For the sign magnitude representation, the MSB is assumed to represent a negative sign if it is equal to one. The excess code is yet another way of representing negative numbers. In excess code, the unsigned value of a bit pattern represents the required number plus a known excess value (sometimes called bias). In the table, the bias equals eight in the first case, seven in the second, and three in the third. Although four bits provide 16 distinct representations, the use of sign-magnitude or ones complement leads to only 15 distinct numbers since there are two equivalent representations of zero in each of those two codes. The two's complement and the excess coding allow the representation of 16 different numbers. However, the range of representable numbers may be changed according to the implicitly assumed bias. Other ways of encoding numbers are possible and we will see more of these as we progress in the book.

| Pattern | Unsigned | S-M  | 1s | 2's | excess-8 | excess-7 | excess-3 |

|---------|----------|------|----|-----|----------|----------|----------|

| 1111    | 15       | -7   | -0 | -1  | 7        | 8        | 12       |

| 1110    | 14       | -6   | -1 | -2  | 6        | 7        | 11       |

| 1101    | 13       | -5   | -2 | -3  | 5        | 6        | 10       |

| 1100    | 12       | -4   | -3 | -4  | 4        | 5        | 9        |

| 1011    | 11       | -3   | -4 | -5  | 3        | 4        | 8        |

| 1010    | 10       | -2   | -5 | -6  | 2        | 3        | 7        |

| 1001    | 9        | -1   | -6 | -7  | 1        | 2        | 6        |

| 1000    | 8        | -0   | -7 | -8  | 0        | 1        | 5        |

| 0111    | 7        | 7    | 7  | 7   | -1       | 0        | 4        |

| 0110    | 6        | 6    | 6  | 6   | -2       | -1       | 3        |

| 0101    | 5        | 5    | 5  | 5   | -3       | -2       | 2        |

| 0100    | 4        | 4    | 4  | 4   | -4       | -3       | 1        |

| 0011    | 3        | 3    | 3  | 3   | -5       | -4       | 0        |

| 0010    | 2        | $^2$ | 2  | 2   | -6       | -5       | -1       |

| 0001    | 1        | 1    | 1  | 1   | -7       | -6       | -2       |

| 0000    | 0        | 0    | 0  | 0   | -8       | -7       | -3       |

Table 1.1: Some binary coding schemes

In complement coding, the bit pattern range is divided in two halves with the upper half (i.e. where the MSB = 1) representing negative values. In excess codes, on the other hand, the bit patterns that look smaller (i.e. their unsigned value is smaller) are in fact less than those that look larger.

**Example 1.8** The mix between the various coding schemes is a common bug for beginners in programing. For example, the following C code shows what we might get

```

if we 'look' at the same bit pattern as unsigned versus if we look at it as signed within the context of a program using 32 bits to represent integers.

#include < stdio . h >

int main(void)

{

int x = 200000000000;

int y = 20000000000;

printf("x = \%d, y = \%d \ ", x, y);

printf("(unsigned) x + y = \%u \ ", x + y);

printf("(signed) x + y = \%d \ ", x + y);

}

Once we compile and run this code the result is:

x = 20000000000, y = 20000000000

```

The sum of x and y in example 1.8 has MSB = 1 which indicates a negative number if the

(unsigned) x+y = 40000000000(signed) x+y = -294967296 programmer is not careful to ask for an unsigned interpretation. In this example, two numbers in the 'lower half' of the range of two's complement representation were summed together. Their sum is in fact a number beyond the lower half and lies within the upper half of the range. If we interpret that sum as a two's complement representation we get the strange result. This is an instance of 'overflow' as we will see in the following section.

## 1.4 Implementation of Integer Operations

For each integer data representation, five operations will be analyzed: addition, subtraction, shifting, multiplication, and division. Most of the discussion assumes binary arithmetic (radix 2).

Addition and subtraction are treated together, since the subtraction is the same as addition of two numbers of opposite signs. Thus, subtraction is performed by adding the negative of the subtrahend to the minuend. Therefore, the first thing to be addressed is the negation operation in each data representation.

#### 1.4.1 Negation

In a ones' complement system, negation is a simple Boolean NOT operation. Negation in a two's complement (**TC**) system can be viewed as

$$TC(N) = 2^n - N = (2^n - 1 - N) + (1),$$

where n is the number of digits in the representation. It may look awkward in the equation, but in practice this form is easier to implement, since the first term is the simple ones' complement (i.e., NOT operation) and the second term calls for adding one to the least significant bit (LSB).

Although we have just described radix complement and diminished radix complement in general terms, it is instructive to re-iterate some of the issues for the special case of a binary radix. For this purpose, we follow the discussion of ones' and two's complement operations provided by Stone [Stone, 1975].

#### 1.4.2 Two's Complement Addition

Two's complement addition is performed as if the two numbers were unsigned numbers; that is, no correction is required. However, it is necessary to determine when an overflow occurs. For two summands P and N, there are four cases to consider:

|   | Case | P        | N        | Comments |

|---|------|----------|----------|----------|

| ĺ | 1    | Positive | Positive |          |

| ١ | 2    | Negative | Negative |          |

|   | 3    | Positive | Negative | P  <  N  |

|   | 4    | Positive | Negative | P  >  N  |

For positive numbers, the sign bit (the *MSB*) is zero, and for negative numbers, the sign bit is one. The sign bit is added just like all the other bits. Thus, the sign bit of the final result is made up of the sum of the summands' sign bits plus the carry into the sign bit.

In the first case, the sum of the sign bits is zero (0 + 0 = 0), and if no carry is generated by the remaining lower order bits, the resultant sign bit is zero. No overflow occurs under this condition. On the other hand, if a carry is generated by the remaining lower order bits, the binary representation of the result does not fit in the number of bits allocated to the summands and the resultant sign bit becomes one. That is, adding two positive summands generates a result surpassing the boundary which separates the negative and positive numbers. The result is falsely interpreted as being negative. An overflow must be signaled under this condition.

The rest of the cases are analyzed in a similar fashion and summarized in the following table:

|      |     |     | $\operatorname{Sum}$ | Carry-in to Sign | Carry-out of     |          |         |

|------|-----|-----|----------------------|------------------|------------------|----------|---------|

| Case | P   | N   | of Signs             | Bit $(C_{n-1})$  | Sign Bit $(C_n)$ | Overflow | Notes   |

| 1a   | Pos | Pos | 0                    | 0                | 0                | no       |         |

| 1b   | Pos | Pos | 0                    | 1                | 0                | yes      |         |

| 2a   | Neg | Neg | 0                    | 1                | 1                | no       |         |

| 2b   | Neg | Neg | 0                    | 0                | 1                | yes      |         |

| 3    | Pos | Neg | 1                    | 0                | 0                | no       | P  <  N |

| 4    | Pos | Neg | 1                    | 1                | 1                | no       | P  >  N |

Two observations can be made from the above table:

- 1. It is impossible to overflow the result when the two summands have different signs (this is quite clear intuitively).

- 2. The overflow condition can be stated in terms of the carries in and out of the sign bit—that is, overflow occurs when these carries are different.

Using  $\oplus$  for the exclusive OR, the XOR, operation, the Boolean expression for the overflow is thus:

OVERFLOW =

$$C_{n-1} \oplus C_n$$

.

#### 1.4.3 Ones Complement Addition

It was mentioned earlier that addition in ones' complement representation requires correction. Another way of looking at the reason for correction is to analyze the four cases as was done for the two's complement addition (for simplicity, the overflow cases are ignored).

Case 1, both P and N are positive: Same as two's complement addition, and no correction is required.

Case 2, both P and N are negative: Remeber that we are using the diminished radix complement ( $\mathbf{DRC}(|x|) = 2^n - 1 - |x|$ ). We want to get  $\mathbf{DRC}(|P| + |N|)$  by adding  $\mathbf{DRC}(|P|) +$

17

$\mathbf{DRC}(|N|)$ . However,

which is not  $\mathbf{DRC}(|P|+|N|)$ . The resulting sum is, in fact, larger than what is possible to represent in n bits and a carry-out of the sign bit occurs. In modulo  $2^n$ , the number  $2^{n+1}$  is represented by its congruent  $2^n$ . Thus, the sum is  $2^n - 2 - (|P| + |N|)$ , whereas we wanted the ones' complement format  $2^n - 1 - (|P| + |N|)$ . Therefore, 1 must be added to the LSB to have the correct result.

Case 3, P is positive, N is negative, and |P| < |N|:

$$\begin{array}{c|cccc} & & |P| \\ + & 2^n - 1 & - & |N| \\ \hline & 2^n - 1 & - & (|N| - |P|) \end{array}$$

This form requires no correction since it gives a result representable in n bits with the correct value.

Case 4, P is positive, N is negative, and |P| > |N|:

$$\begin{array}{c|ccccc} & & |P| \\ + & 2^n - 1 & - & |N| \\ \hline & 2^n - 1 & + & (|P| - |N|) \end{array}$$

Since |P| > |N|, this result is positive and in the modulo  $2^n$  system a carry-out of the sign bit is generated leaving a result congruent to -1 + (|P| - |N|). Hence, a correction is required.

The implementation of the correction term is relatively easy. In both cases when a correction is necessary there is a carry-out of the sign bit. In the other two cases, this carry-out is zero. Thus, in hardware, the carry-out of the sign bit is added to the LSB (if no correction is required, zero is added to the LSB). The correction term is the end-around carry, and it causes ones' complement addition to be slower than two's complement addition.

Overflow detection in one's complement addition is the same as in two's complement addition; that is, OVERFLOW =  $C_{n-1} \oplus C_n$ .

#### 1.4.4 Computing Through the Overflows

This subject is covered in detail by Garner [Garner, 1978]. Here, we just state the main property. In complement-coded arithmetic, it is possible to perform a chain of additions, subtractions, multiplications, or any combination that will generate a final correct (representable) result, even though some of the intermediate results have overflowed.

**Example 1.9** In 4-bit two's complement representation, where the range of representable numbers is -8 to +7, consider the following operation:

$$+5+4-6=+3. \\ 0101 +5 \\ 0100 +4 \\ \hline 1001 \text{ Overflow} \\ 1010 -6 \\ \hline 0011 +3 \text{ (correct)} \\ \\ \end{array}$$

The important condition allowing us to neglect the intermediate overflows is that the final result is bound to a representable value. In fact, the computation through the overflow follows from the properties of modular arithmetic:

$$\begin{aligned} &(A\left[+,-,\times\right]B\left[+,-,\times\right]C\left[+,-,\times\right]D)\mathbf{mod}_{\mu} \\ &= ((A\left[+,-,\times\right]B\left[+,-,\times\right]C)\mathbf{mod}_{\mu}\left[+,-,\times\right]D\mathbf{mod}_{\mu})\,\mathbf{mod}_{\mu} \\ &= (((A\left[+,-,\times\right]B)\mathbf{mod}_{\mu}\left[+,-,\times\right]C\mathbf{mod}_{\mu})\,\mathbf{mod}_{\mu}\left[+,-,\times\right]D\mathbf{mod}_{\mu})\,\mathbf{mod}_{\mu} \end{aligned}$$

If the final result is representable then the intermediate results may be computed  $\mathbf{mod}_{\mu}$  without affecting the correctness of the operations.

#### 1.4.5 Arithmetic Shifts

The arithmetic shifts are discussed as an introduction to the multiplication and division operations. An arithmetic left shift is equivalent to multiplying by the radix (assuming the shifted result does not overflow), and an arithmetic right shift is equivalent to dividing by the radix. In binary, shifting p places is equivalent to multiplying or dividing by  $2^p$ . In left shifts (multiplying), zeros are shifted into the least significant bits, and in right shifts, the sign bit is shifted into the most significant bit (since the quotient will have the same sign as the dividend).

```

Example 1.10 Perform both a left and a right shift by three bits on the binary number 0001\,0110 = 22 and check the results.

Solution: After a left shift by two we get 1011\,0000. If the numbers are unsigned then 1011\,0000 = 176 which is the expected result (= 2^3 \times 22). However, if the numbers are signed numbers in two's complement format then the operation has caused an overflow. For the case of a right shift, we get 0000\,0010 = 2 which is the integer part of 22/(2^3).

```

The difference between a logical and an arithmetic shift is important to note. In a logical shift, all bits of a word are shifted right or left by the indicated amount with zeros filling unreplaced end bits. In an arithmetic shift, the sign bit is fixed and the sign convention must be observed when filling unreplaced end bits. Thus, a right shift (divide) of a number will fix the sign bit and fill the higher order unreplaced bits with either ones or zeros in accordance with the sign bit. With arithmetic left shift, the lower order bits are filled with zeros regardless of the sign bit.

As illustrated by the previous example, so long as a p place left shift does not cause an overflow—i.e.,  $2^p$  times the original value is less than or equal to the maximum representable number in the word—arithmetic left shift is the same as logical left shift.

19

**Example 1.11** What is the effect of a three bit arithmetic left and right shift on  $1111\,0111 = -9$  and  $1110\,0101 = -27$ ? What if the shifts are logical? *Solution:* The results of the four kinds of shifting are

|     | Arith. Left    | Arith. Right   | Logic Left     | Logic Right    |

|-----|----------------|----------------|----------------|----------------|

|     | $\times 2^3$   | $\div 2^3$     | Shift by 3     | Shift by 3     |

| -9  | 10111000 = -72 | 111111110 = -2 | 10111000 = -72 | 00011110 = +30 |

| -27 | 10101000 = -88 | 111111100 = -4 | 00101000 = +40 | 00011100 = +28 |

It is quite clear that logical right shifts produce wrong results for two's complement negative numbers. Only the arithmetic right shifts are useful if we are implementing complement coding.

For left shifts, both arithmetic and logical shifts produce the same results for -9 since no overflow occurs. However, the difference is evident in the case of -27.

We notice something from this last example: in two's complement arithmetic right shift, there is an asymmetry between the shifted results of positive and negative numbers:

$$\begin{array}{cccc} -13 = 1\,0011 & \stackrel{1 \text{ bit right shift}}{\rightarrow} & 1\,1001 = -7; \\ +13 = 0\,1101 & \stackrel{1 \text{ bit right shift}}{\rightarrow} & 0\,0110 = +6. \end{array}$$

This, of course, relates to the asymmetry of the two's complement data representation, where the quantity of negative numbers is larger by one than the quantity of positive numbers.

By contrast, the ones' complement right shift is symmetrical:

$$-13 = 1\,0010 \quad \stackrel{\text{1 bit right shift}}{\rightarrow} \quad 1\,1001 = -6;$$

$$+13 = 0\,1101 \quad \stackrel{\text{1 bit right shift}}{\rightarrow} \quad 0\,0110 = +6.$$

Notice that the asymmetric resultant quotients correspond to modular division—i.e., creating a quotient so that the remainder is always positive. Similarly, symmetric quotients correspond to signed division—the remainder assumes the sign of the dividend.

#### 1.4.6 Multiplication

In unsigned data representation, multiplying two operands, one with n bits and the other with m bits, requires that the result will be n+m bits. If each of the two operands is n bits, then the product has to be 2n bits. This, of course, corresponds to the common notion that the multiplication product is a double-length operand.

Exercise 1.10 Prove that 2n bits are necessary to correctly represent the product P of two unsigned n bits operands.

In signed numbers, where the MSB of each of the operands is a sign bit, the product should require only 2n-1 bits, since the product has only one sign bit. However, in the two's complement code there is one exceptional case: multiplying  $-2^n$  by  $-2^n$  results in  $+2^{2n}$ . But this positive number is not representable in 2n-1 bits. This latter case is often treated as an overflow, especially in fractional representation when both operand and results are restricted to the range [-1, +1[. Thus, multiplying  $-1 \times -1$  gives the unrepresentable +1.

#### 1.4.7 Division

Division is the most difficult operation of the four basic arithmetic operations. Two properties of the division are the source for this difficulty:

- 1. Overflow—Even when the dividend is n bits long and the divisor is n bits long, an overflow may occur. A special case is a zero divisor.

- 2. Inaccurate results—In most cases, dividing two numbers gives a quotient that is an approximation to the actual rational number.

In general, one would like to think of division as the converse operation to multiplication but, by definition:

$$\begin{array}{rcl} \frac{a}{b} & = & q + \frac{r}{b}, \\ a & = & b \times q + r, \end{array}$$

where a is the dividend, b is the divisor, q is the quotient, and r is the remainder. In the subset of cases when r = 0, the division is the exact converse of multiplication.

In terms of the natural integers (Peano's numbers), all multiplication results are still integers, but only a small subset of the division results are such numbers. The rest of the results are rational numbers, and to represent them accurately a pair of integers is required.

In terms of machine division, the result must be expressed by one finite number. Going back to the definition of division,

$$\frac{a}{b} = q + \frac{r}{b},$$

we observe that the same equation holds true for any desired finite precision.

**Example 1.12** In decimal arithmetic, if a = 1, b = 7, then 1/7 is computed as follows:

The multiplicity of valid results is a difficulty in division. This multiplicity depends on the sign conventions, e.g., signed versus modular division. Recall that  $-7 \div_m 3 = -3$  while  $-7 \div_s 3 = -2$ . Thus, if the hardware provides modular division using two's complement code and one wishes a signed division, a negative quotient requires a correction by adding one to the least significant bit.

Multiplication can be thought of as successive additions, and division is similarly successive subtractions. However, in multiplication it is known how many times to add, in division the quotient digits are not known in advance. It is not absolutely certain how many times it will be necessary to subtract the divisor from a given order of the dividend.

**Example 1.13** If we divide 01111 by 00100 through successive subtractions we get:

| •                    | v                           | o o                        | O |

|----------------------|-----------------------------|----------------------------|---|

| Iteration            | Remainder                   | Is the remainder negative? |   |

| 1                    | 01111 - 00100 = 01011       | no                         |   |

| 2                    | 01011 - 00100 = 00111       | no                         |   |

| 3                    | 00111 - 00100 = 00011       | no                         |   |

| 4                    | 00011 - 00100 = 11111       | $yes \Rightarrow Stop$     |   |

|                      |                             |                            |   |

| which means that the | e result is 3 in decimal or | 00011 in binary.           |   |

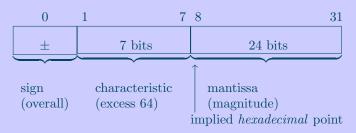

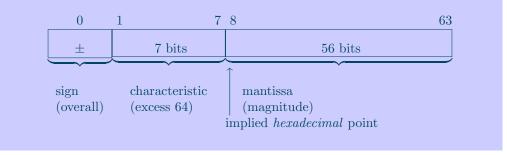

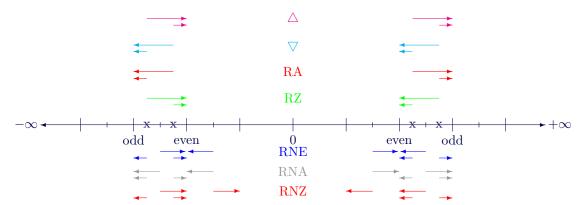

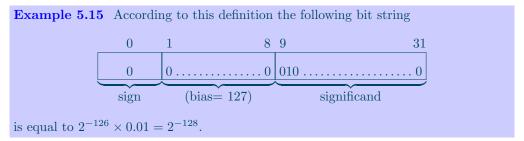

As the example shows, in these algorithms, which are trial and error processes, it is not known that the divisor has been subtracted a sufficient number of times until it has been subtracted once too often. In implementing a simple subtractive division algorithm, the lack of knowledge regarding the number of subtractions to perform in the division becomes evident. Several subtractive techniques exist with varying complexities and time delays.