# Power/Energy Estimation and Optimization for Software-Oriented Embedded Systems

by

Mostafa Elsayed Ahmed Ibrahim

Electrical Engineering Department

High Institute of Technology

Benha University

Thesis Submitted to the

Faculty of Engineering at Cairo University, Egypt

in Partial Fulfillment of the

Requirements for the Degree of

Doctor of Philosophy

in

Electronics and Electrical Communications Engineering

Faculty of Engineering - Cairo University

Giza, Egypt

November, 2009

# Power/Energy Estimation and Optimization for Software-Oriented Embedded Systems

by

## Mostafa Elsayed Ahmed Ibrahim

Thesis Submitted to the

Faculty of Engineering at Cairo University, Egypt

in Partial Fulfillment of the

Requirements for the Degree of

**Doctor of Philosophy**

in

Electronics and Electrical Communications Engineering

## Supervised by

## **Prof. Dr. Serag-Eldin Elsayed Habib**

Electronics and Communication Department Faculty of Engineering - Cairo University

## Prof. Dr. Markus Rupp

Institute of Communications and Radio-Frequency Engineering Vienna University of Technology

## Dr. Hossam A. H. Fahmy

Electronics and Communication Department Faculty of Engineering - Cairo University

Faculty of Engineering - Cairo University

Giza, Egypt

November, 2009

# Power/Energy Estimation and Optimization for Software-Oriented Embedded Systems

# by **Mostafa Elsayed Ahmed Ibrahim**

Thesis Submitted to the

Faculty of Engineering at Cairo University, Egypt

in Partial Fulfillment of the

Requirements for the Degree of

**Doctor of Philosophy**

in

Electronics and Electrical Communications Engineering

| Approved by the Examining Committee:                                                          |

|-----------------------------------------------------------------------------------------------|

| Prof. Dr. Mohamed Zaki Abd El Mageed, Member                                                  |

| Faculty of Engineering - Al Azhar University                                                  |

| Prof. Dr. Ashraf ElFarghaly Salem, Member Faculty of Engineering - Ain Shams University       |

| Prof. Dr. Serag-Eldin Elsayed Habib, Thesis advisor                                           |

| Faculty of Engineering - Cairo University                                                     |

| Prof. Dr. Markus Rupp, Thesis advisor                                                         |

| Faculty for Electrical Engineering and Information Technology Vienna University of Technology |

Faculty of Engineering - Cairo University

Giza, Egypt

November, 2009

## **ABSTRACT**

The importance of power reduction of embedded systems has continuously increased in the past years. Recently, reducing power dissipation and energy consumption of a program have become optimization goals in their own right, no longer considered a side-effect of traditional performance optimizations which mainly target program execution time and/or program size. Nowadays, there is an increasing demand for developing power-optimizing compilers for embedded systems. This thesis is a step towards such important goal.

In this thesis, we develop functional-level power models and investigate several software optimization techniques for embedded-processor systems. As a specific example, we consider the powerful Texas Instruments C6416T DSP processor. We analyze the power consumption contributions of the different functional units of this DSP. We assess the effect of the compiler performance optimizations on the energy and power consumption. Moreover, we explore the impact of two special architectural features of this DSP; namely Software Pipelined Loop (SPLOOP) and the SIMD capabilities, on the energy and power consumption.

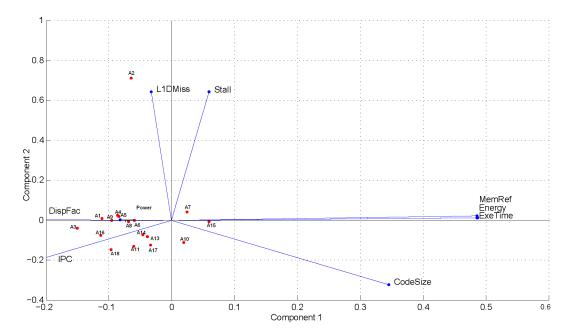

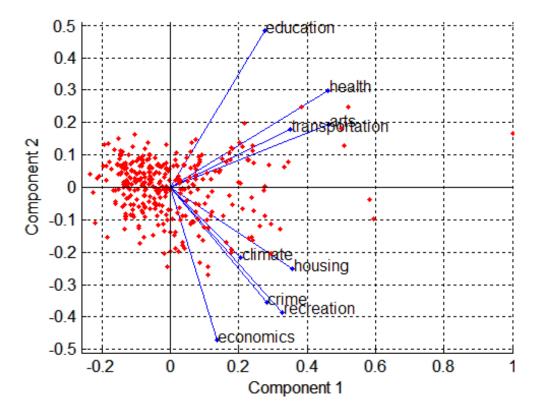

We also characterize the application-architecture correlation for our targeted architecture. The PCA multivariate statistical technique is employed to visualize the black box impact of the compiler and the hardware architecture over the software applications. This is achieved with the aid of biplots which is depicted in our analysis in such a way, so that it can show the maximum association between the application and the underlying hardware architecture. Hence, it answers the question whether a given hardware architecture is an appropriate choice for a given software application or not.

The currently-available compiler optimization techniques are handicapped for power optimization due to their partial perspective of the algorithms and due to their limited modifications to the data structures. On the contrary, other software optimization techniques, like source code transformations, can exploit the full knowledge of the algorithm characteristics, with the capability of modifying both data structures and algorithm coding. Furthermore, inter-procedural optimizations are envisioned. Hence, we investigate several loop, data and procedural source code transformations from the power and energy perspectives.

Based on our results and as a step towards a power-aware optimizing compiler, we can recommend the following recommendations for programmers and compiler designers. *First*,

viii Abstract

the programmers, targeting the C6000 DSP family, are strongly recommended to compile and optimize their programs by invoking the optimization level -o3 while disabling the SPLOOP feature (-mu) in conjunction with the utilization of SIMD capabilities via the employment of suitable intrinsic functions.

**Second,** we recommend the compiler designers to pay more attention to the circular (modulo) and bit reverse addressing schemes which are rarely utilized by the compiler. In addition, they should utilize the power-aware source code transformations.

*Third*, developers of power simulators need to embed a functional level power consumption model for the target processor in their simulators software.

## **ACKNOWLEDGEMENTS**

As the author of this thesis, I am keenly aware that it represents the fruition of not only my own work, but also the support which other individuals and organizations have lent me over the years, and for which I am profoundly grateful.

First, I would like to thank my advisors, Prof. Serag E.-D Habib, Prof. Markus Rupp, and Dr. Hossam A. H. Fahmy for their support, advice, guidance, and good wishes. They have had a profound influence not only as my PhD advisors, but also on my life. Their availability at all times, dedication towards work and family, professional integrity, and pursuit of perfection helped me becoming a better individual. I am grateful to them for the freedom and flexibility they gave me during the hard PhD years I spent in both Cairo and Vienna.

I would like to express the greatest of gratitude to my parents as well as my brothers and sisters for the extraordinary way they provide me with unfaltering support, encouragement, and love, even when I am far away from them. Finally, I offer special thanks and appreciations to my wife and kids, for their love, understanding, and inexhaustible kindness.

I would like to thank the members (past and current) at the Christian Doppler Laboratory (CD Lab.) for Design Methodology of Signal Processing Algorithms Bastian Knerr, Martin Holzer, and Christoph Angerer who passed on valuable comments on drafts of my paper submissions during all stages of my research.

I would like to thank Dr. Mohammad Bakr for the fruitful discussions and for providing me with some helpful papers during my PhD years.

## **CONTENTS**

| 1 | Intro                | roduction |                                                           |    |  |  |

|---|----------------------|-----------|-----------------------------------------------------------|----|--|--|

|   | 1.1 Embedded Systems |           |                                                           |    |  |  |

|   |                      | 1.1.1     | Target Architectures for Embedded Systems                 | 2  |  |  |

|   |                      | 1.1.2     | Embedded Systems Design Metrics                           | 6  |  |  |

|   | 1.2                  | Motiva    | ation                                                     | 10 |  |  |

|   | 1.3                  | Contri    | butions                                                   | 11 |  |  |

|   | 1.4                  | Thesis    | Outline                                                   | 13 |  |  |

| 2 | Rela                 | ted Wo    | rk                                                        | 17 |  |  |

|   | 2.1                  | Introd    | uction                                                    | 17 |  |  |

|   | 2.2                  | Softwa    | are Power Consumption Estimation Techniques               | 17 |  |  |

|   |                      | 2.2.1     | Low-Level Estimation Techniques                           | 18 |  |  |

|   |                      | 2.2.2     | High-Level Estimation Techniques                          | 22 |  |  |

|   | 2.3                  | Power     | Saving Techniques: Overview                               | 25 |  |  |

|   |                      | 2.3.1     | Manufacturing Level Power Saving                          | 25 |  |  |

|   |                      | 2.3.2     | Processor Level Power Saving                              | 26 |  |  |

|   |                      | 2.3.3     | Dynamic Voltage and Frequency Scaling                     | 27 |  |  |

|   |                      | 2.3.4     | Battery Aware Power Saving                                | 28 |  |  |

|   |                      | 2.3.5     | Compiler Level Power Saving                               | 29 |  |  |

|   | 2.4                  | Source    | e to Source Code Transformations                          | 31 |  |  |

|   | 2.5                  | Conclu    | usions                                                    | 33 |  |  |

| 3 | Prec                 | ise Pow   | ver Consumption Model                                     | 35 |  |  |

|   | 3.1                  | Introd    | uction                                                    | 35 |  |  |

|   | 3.2                  | Experi    | imental Setup                                             | 36 |  |  |

|   | 3.3                  | Metho     | dology                                                    | 37 |  |  |

|   |                      | 3.3.1     | Static and Clock Distribution Power Consumption Sub-Model | 39 |  |  |

|   |                      | 3.3.2     | IMU Power Consumption Sub-Model                           | 40 |  |  |

|   |                      | 3.3.3     | PU Power Consumption Sub-Model                            | 42 |  |  |

|   |                      | 3.3.4     | Internal Memory Power Consumption Sub-Model               | 44 |  |  |

xii Contents

|   |     | 3.3.5                 | L1 Data Cache Power Consumption Sub-Model                           | 46  |

|---|-----|-----------------------|---------------------------------------------------------------------|-----|

|   |     | 3.3.6                 | L1 Program Cache Power Consumption Sub-Model                        | 47  |

|   | 3.4 | Model                 | Validation                                                          | 49  |

|   |     | 3.4.1                 | Validation with Benchmarks                                          | 49  |

|   |     | 3.4.2                 | Validation with a Real Application                                  | 51  |

|   | 3.5 | Conclu                | asions                                                              | 56  |

| 4 | Com | npiler O <sub>l</sub> | ptimization Influence on the Energy and Power Consumption           | 57  |

|   | 4.1 | Introdu               | uction                                                              | 57  |

|   | 4.2 | Target                | ed Compiler and Applications                                        | 58  |

|   | 4.3 | Global                | Performance Optimizations Effects on power and Energy               | 59  |

|   |     | 4.3.1                 | Optimizations Effect on Other Execution Characteristics             | 62  |

|   | 4.4 | Specifi               | ic Architectural and Compiler Features Effects on Power and Energy. | 65  |

|   |     | 4.4.1                 | Impact of Software Pipelined Loop                                   | 65  |

|   |     | 4.4.2                 | Impact of SIMD                                                      | 69  |

|   | 4.5 | Charac                | eterization of Application-Architecture Correlation                 | 75  |

|   | 4.6 |                       | asions                                                              | 79  |

| _ |     |                       |                                                                     |     |

| 5 | •   |                       | ource Code Transformations on Energy and Power                      | 81  |

|   | 5.1 | Introdu               | uction                                                              | 81  |

|   | 5.2 | Loop (                | Oriented Transformations                                            | 82  |

|   |     | 5.2.1                 | Loop Reversal                                                       | 82  |

|   |     | 5.2.2                 | Loop-Based Strength Reduction                                       | 83  |

|   |     | 5.2.3                 | Loop Unswitching                                                    | 85  |

|   |     |                       | Loop Permutation                                                    | 86  |

|   |     | 5.2.5                 | Loop Peeling                                                        | 87  |

|   |     | 5.2.6                 | Loop Fusion                                                         | 88  |

|   |     | 5.2.7                 | Loop Peeling and Fusion                                             | 89  |

|   |     | 5.2.8                 | Loop Normalization and Fusion                                       | 90  |

|   |     | 5.2.9                 | Loop Unrolling                                                      | 91  |

|   |     |                       | Loop Tiling                                                         | 93  |

|   | 5.3 |                       | Oriented Transformations                                            | 94  |

|   |     | 5.3.1                 | Array Declaration Sorting                                           | 94  |

|   |     | 5.3.2                 | Array Elements Scalarization                                        | 95  |

|   | 5.4 |                       | lural and Inter-Procedural Transformations                          | 96  |

|   |     | 5.4.1                 | Procedure Call Preprocessing                                        | 96  |

|   |     | 5.4.2                 | Procedure Integration                                               | 98  |

|   | 5.5 | Conclu                | asions                                                              | 100 |

| Contents | xiii |

|----------|------|

|          |      |

| 6            | Cone   | clusions                                                     | 103 |

|--------------|--------|--------------------------------------------------------------|-----|

|              | 6.1    | Summary and Conclusions                                      | 103 |

|              | 6.2    | Remarks for Future Work                                      | 106 |

| Re           | eferen | ces                                                          | 107 |

| $\mathbf{A}$ | ppen   | ndices                                                       | 119 |

| A            | C64    | 16T Architecture and Profiler Events                         | 121 |

|              | A.1    | Target Architecture                                          | 122 |

|              | A.2    | C6416T Simulator Performance Monitoring Events               | 124 |

| В            | Pow    | er Estimation Details                                        | 127 |

|              | B.1    | Computation of the Model Parameters                          | 127 |

|              | B.2    | Complete Functional-Level Power Consumption Model at 1000MHz | 127 |

|              | B.3    | Power Estimation for Benchmarks                              | 128 |

| C            | Mult   | tivariate Statistics                                         | 131 |

|              | C.1    | Principal Component Analysis (PCA)                           | 131 |

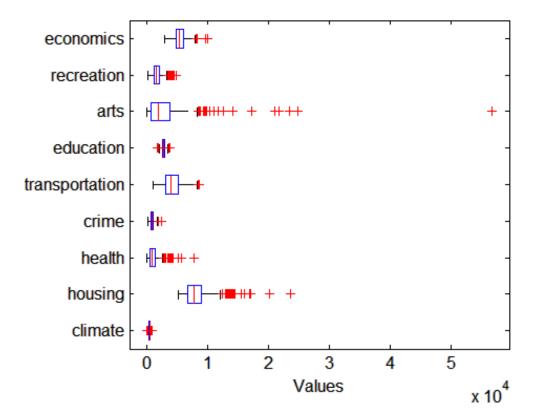

|              |        | C.1.1 Box Plot                                               | 131 |

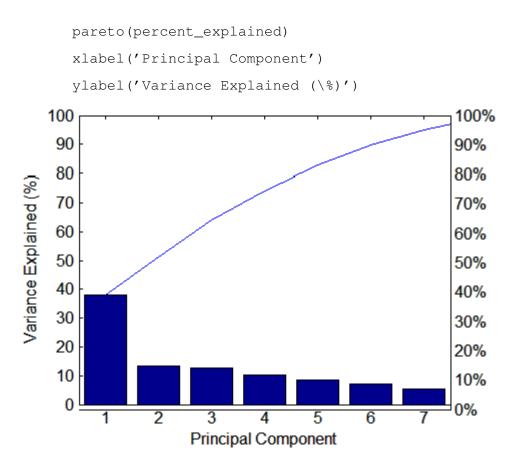

|              |        | C.1.2 Scree Plot                                             | 132 |

|              |        | C.1.3 Biplot                                                 | 132 |

|              |        | C.1.4 PCA Example                                            | 133 |

|              | C.2    | Applications Pseudonyms                                      | 136 |

| D            | List   | of Acronyms                                                  | 139 |

## LIST OF FIGURES

| 1.1  | Architectural components and their affiliation to hardware and software                                                      | 2  |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | NRE and production volume influence on the product unit cost                                                                 | 9  |

| 1.3  | Time-to-Market design metrics impact on the market revenue                                                                   | ç  |

| 1.4  | Embedded systems in automotive electronics                                                                                   | 10 |

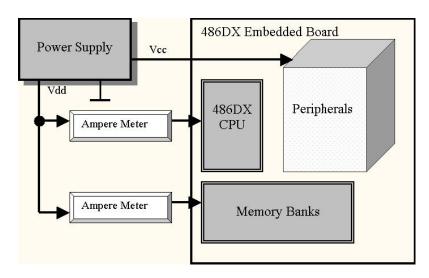

| 2.1  | Experimental Setup for current measurement of V. Tiwari et al                                                                | 23 |

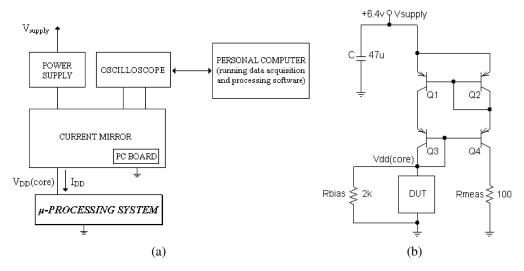

| 2.2  | (a) Experimental Setup for current measurement, (b) The simple current mirror. DUT is the Device Under Test Nilolaidis et al | 24 |

| 2.3  | Functional level power estimation general methodology                                                                        | 25 |

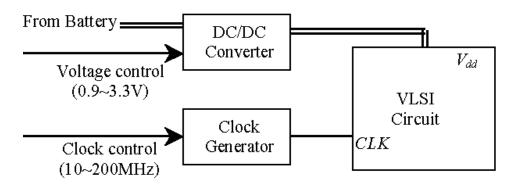

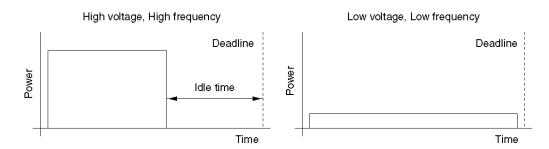

| 2.4  | Dynamic voltage scaling example                                                                                              | 27 |

| 2.5  | Power consumption without and with dynamic voltage and frequency scaling.                                                    | 28 |

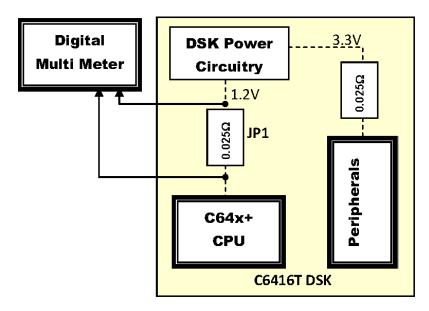

| 3.1  | Current Measurement Setup                                                                                                    | 37 |

| 3.2  | Function level power modeling steps                                                                                          | 38 |

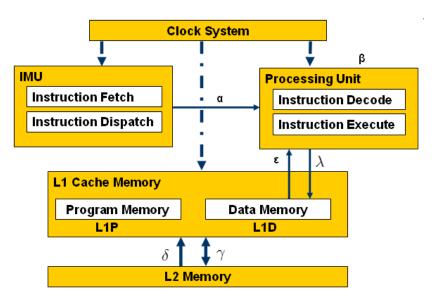

| 3.3  | Functional level power analysis for C6416T                                                                                   | 39 |

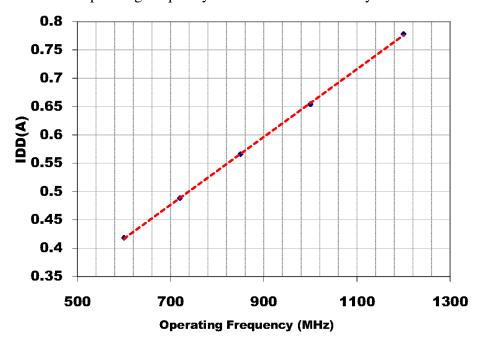

| 3.4  | Model function of the C6416T clock tree                                                                                      | 40 |

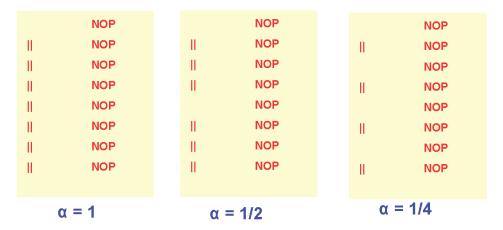

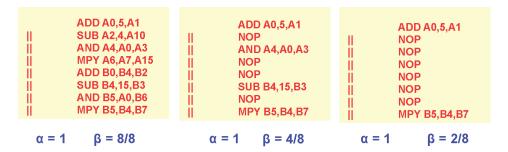

| 3.5  | Screen shots of the scenarios for varying $\alpha$                                                                           | 41 |

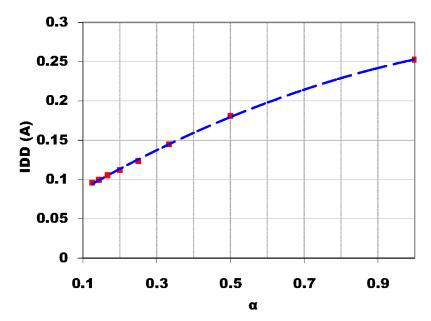

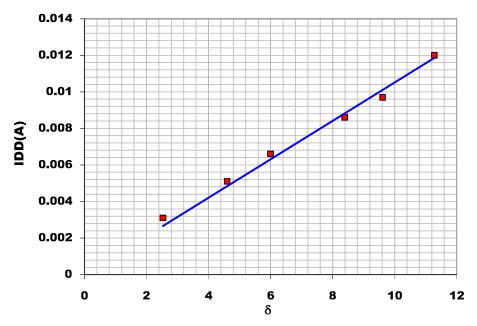

| 3.6  | Model function of the C6416T IMU at $F=1000$ MHz                                                                             | 41 |

| 3.7  | Model function of the C6416T IMU at different frequencies                                                                    | 42 |

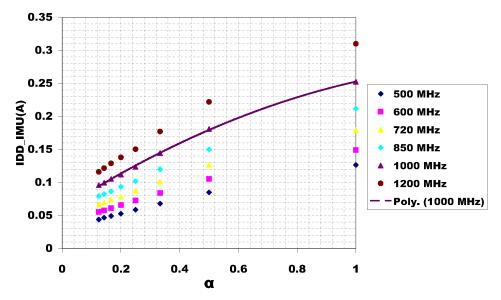

| 3.8  | Difference between $\beta$ and $\alpha$                                                                                      | 43 |

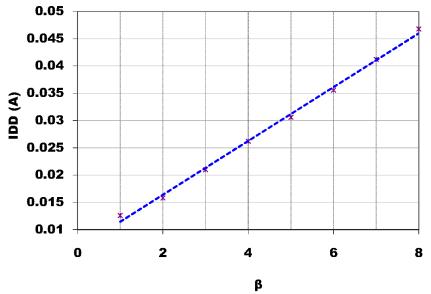

| 3.9  | Model function of the C6416T Processing Units at $\alpha=1$ and $F=1000$ MHz.                                                | 43 |

| 3.10 | Snapshots of different scenarios for varying $\varepsilon$                                                                   | 44 |

xvi List of Figures

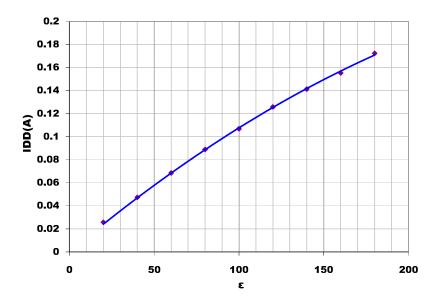

| 3.11 | Model function of the C64161 internal memory read at $\alpha = 1$ and $F = 1,000$ MHz                         | 45 |

|------|---------------------------------------------------------------------------------------------------------------|----|

|      | 1 000MHz                                                                                                      |    |

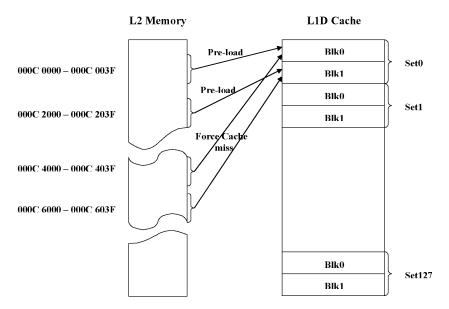

| 3.12 | Scenario for forcing a data cache miss                                                                        | 46 |

| 3.13 | L1D cache miss rate vs. measured CPU current                                                                  | 46 |

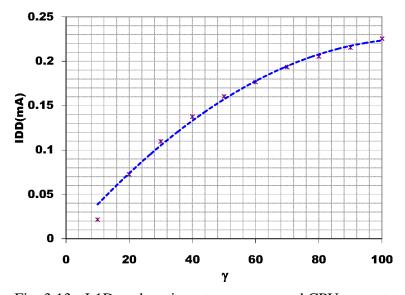

| 3.14 | L1P cache miss rate vs measured CPU current                                                                   | 48 |

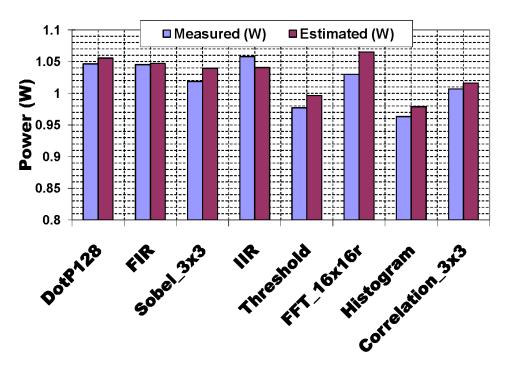

| 3.15 | Estimated vs. measured power consumption of the C6416T at $F=1000 \mathrm{MHz}$ .                             | 51 |

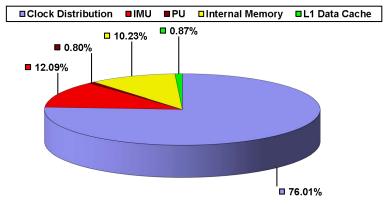

| 3.16 | Average functional units contribution to the processor power consumption                                      | 51 |

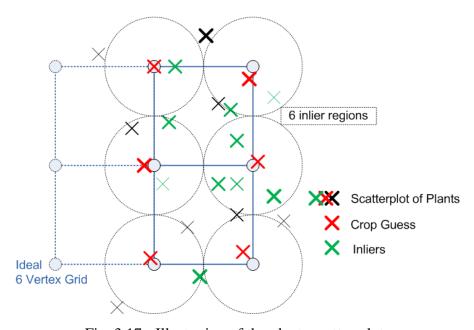

| 3.17 | Illustration of the plants scatter-plot                                                                       | 52 |

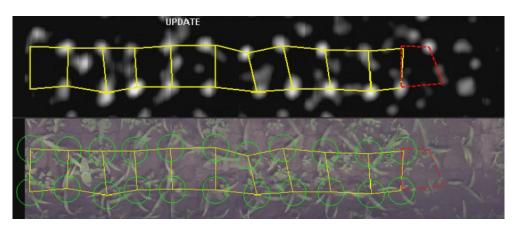

| 3.18 | Elastic graph matching algorithm.                                                                             | 53 |

| 4.1  | Power consumption of the C6416T while running different benchmarks                                            | 59 |

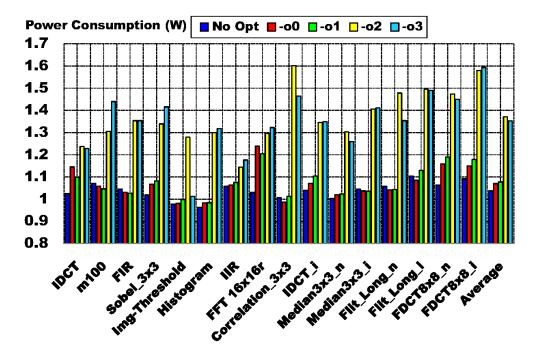

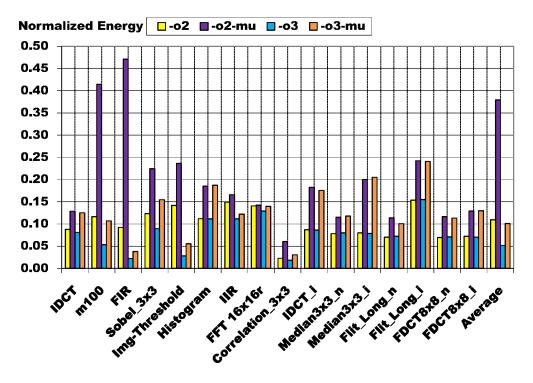

| 4.2  | Normalized Energy versus various optimization options                                                         | 60 |

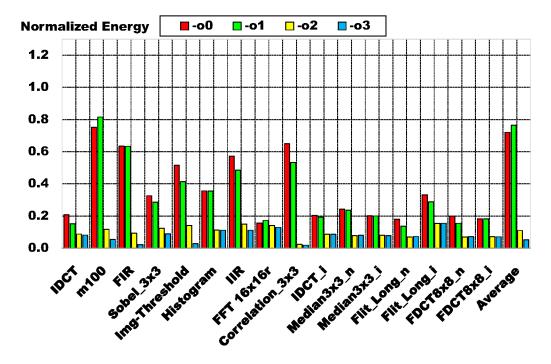

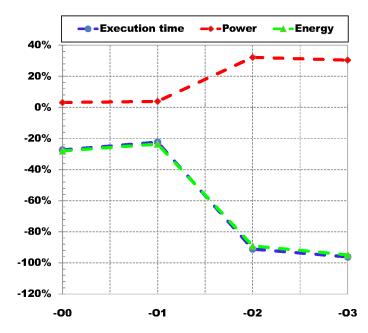

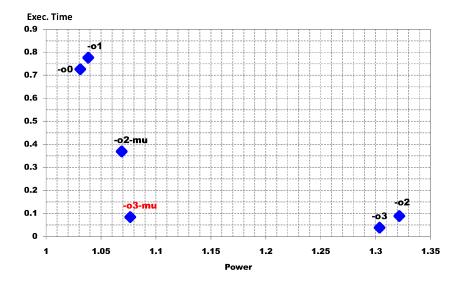

| 4.3  | Power, Execution Time and Energy normalized refering to no optimization versus different optimization options | 61 |

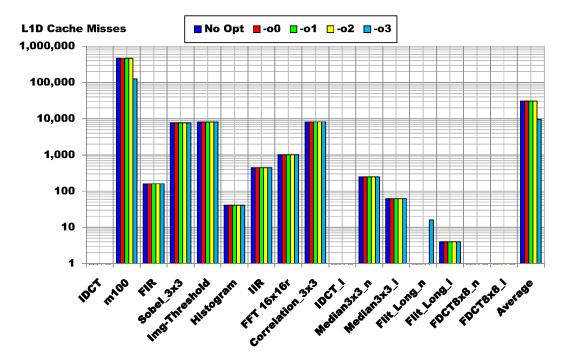

| 4.4  | Impact of optimizations on the L1D cache misses                                                               | 62 |

| 4.5  | CPU stall cycles versus different optimization options                                                        | 63 |

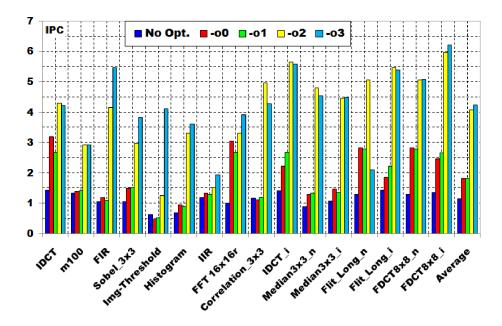

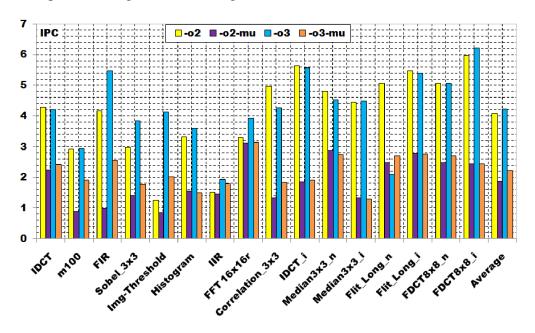

| 4.6  | Effect of various optimization options on the instructions per cycle                                          | 64 |

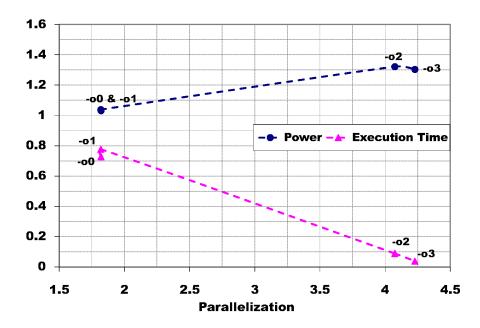

| 4.7  | Parallelization impact on the execution time and the power consumption                                        | 64 |

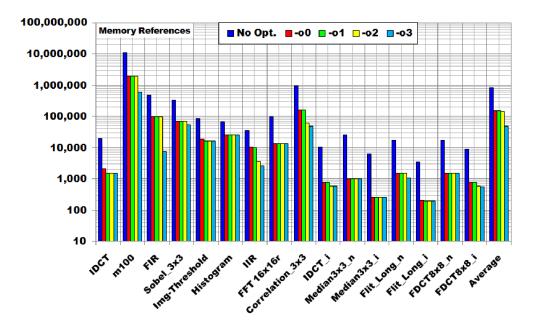

| 4.8  | Effect of different optimization options on the Memory accesses                                               | 65 |

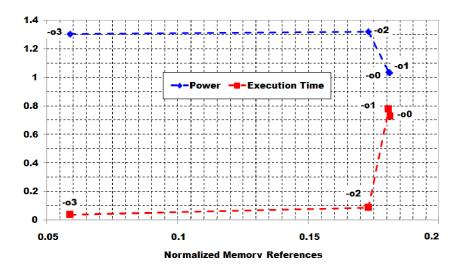

| 4.9  | Memory references impact on the power as well as the execution time                                           | 65 |

| 4.10 | Concept of the SPLOOP                                                                                         | 66 |

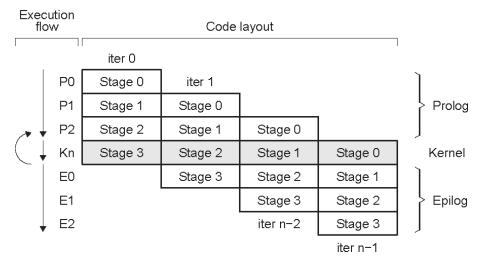

| 4.11 | various optimizations versus execution cycles                                                                 | 67 |

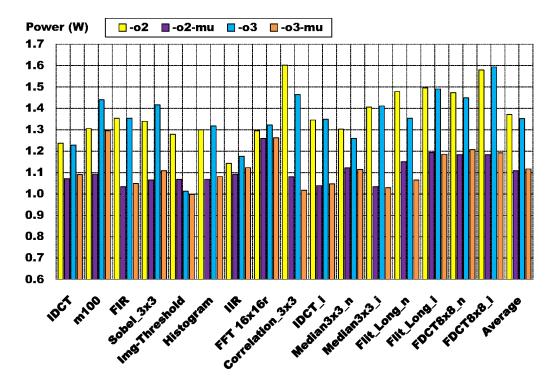

| 4.12 | Impact of SPLOOP on the consumed power                                                                        | 68 |

| 4.13 | Impact of SPLOOP on the energy usage                                                                          | 68 |

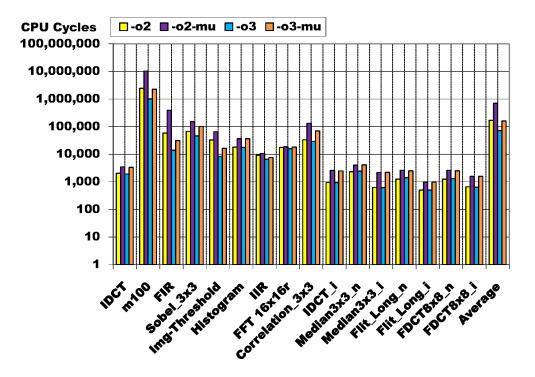

| 4.14 | SPLOOP effect on IPC                                                                                          | 69 |

| 4.15 | Execution time vs. power consumption with various optimization levels                                         | 70 |

| 4.16 | An example of the IDCT kernel w/wo SIMD utilization                                                           | 71 |

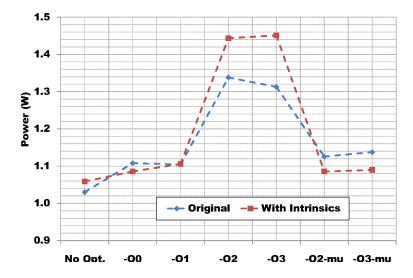

| 4.17 | Power consumption w/wo SIMD utilization vs. various optimization options.                                     | 73 |

List of Figures xvii

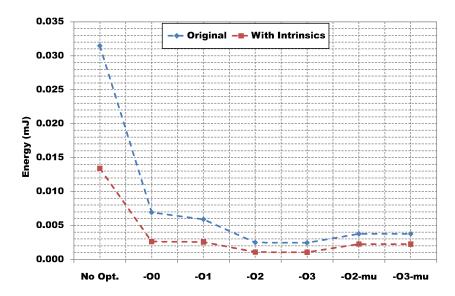

| 4.18 Energy w/wo SIMD utilization vs. various optimization options           | 74  |

|------------------------------------------------------------------------------|-----|

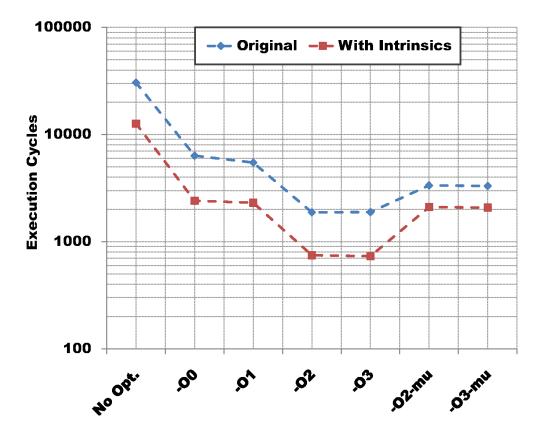

| 4.19 Execution cycles w/wo SIMD utilization vs. various optimization options | 75  |

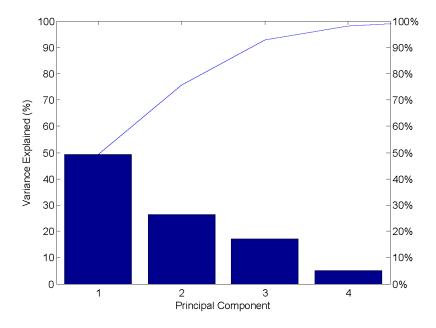

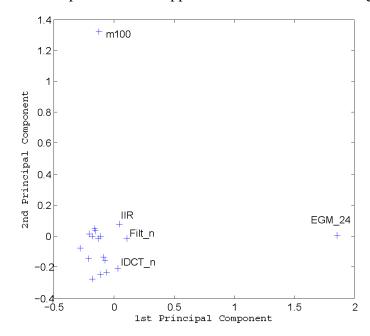

| 4.20 scree plot for the 18 applications at the C6416T using PCA              | 76  |

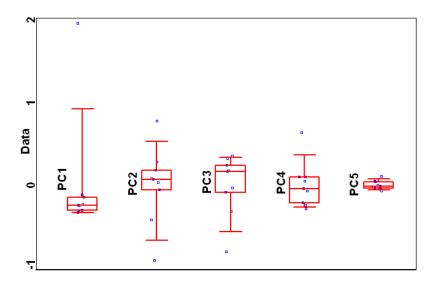

| 4.21 Box plot for the 18 applications at the C6416T using PCA                | 77  |

| 4.22 Plot for the 18 applications data vs. the first two PCs                 | 77  |

| 4.23 biplot for the 18 applications at the C6416T using PCA                  | 78  |

| 5.1 Loop index reversal transformation                                       | 83  |

| 5.2 Loop-based strength reduction transformation                             | 84  |

| 5.3 Loop unswitching transformation                                          | 85  |

| 5.4 Loop permutation transformation                                          | 87  |

| 5.5 Loop peeling transformation                                              | 88  |

| 5.6 Loop fusion transformation                                               | 89  |

| 5.7 Loop peeling and then fusion transformations                             | 90  |

| 5.8 Loop normalization and then fusion transformations                       | 91  |

| 5.9 Loop unrolling transformation with unrolling factor of 8                 | 92  |

| 5.10 Loop tiling transformation                                              | 93  |

| 5.11 Array declaration sorting transformation                                | 95  |

| 5.12 Array elements scalarization transformation                             | 96  |

| 5.13 Procedure call preprocessing transformation                             | 97  |

| 5.14 Procedure integration transformation                                    | 99  |

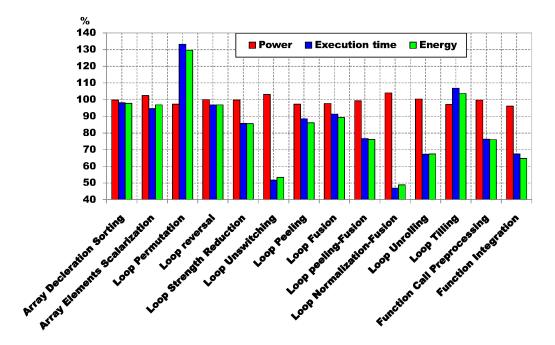

| 5.15 Code transformations impact on power, execution time and energy         | 100 |

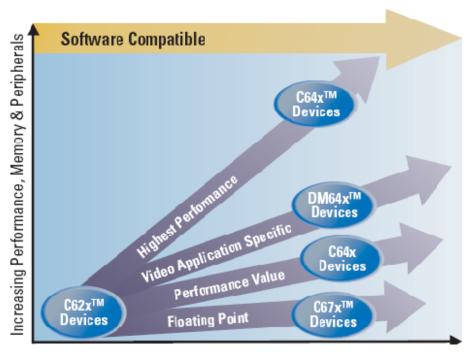

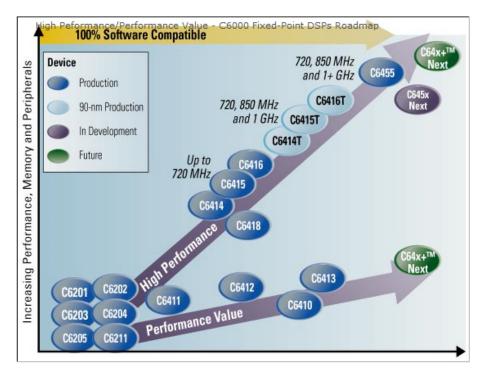

| A.1 C6000 DSP platform roadmap                                               | 121 |

| A.2 C6000 fixed-point DSPs roadmap                                           | 122 |

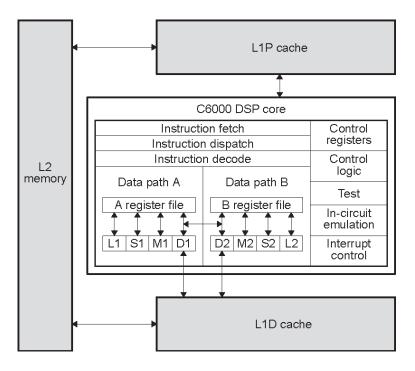

| A.3 C6416 block diagram                                                      | 123 |

| C.1 Box plot for the data ratings                                            | 134 |

| XV111    | L 19 | st of i | H1011  | res |

|----------|------|---------|--------|-----|

| /X V 111 |      | ot OI.  | 1 15 4 | 100 |

| C.2 | Scree plot of the percent variability explained by each principal component. | 135 |

|-----|------------------------------------------------------------------------------|-----|

| C.3 | Visualizing the results of the PCA with the Biplot                           | 136 |

## LIST OF TABLES

| 2.1 | Power saving techniques for embedded systems                                     | 26 |

|-----|----------------------------------------------------------------------------------|----|

| 3.1 | Algorithmic parameters calculation methodology                                   | 48 |

| 3.2 | Complete power consumption model for C6416T DSP                                  | 49 |

| 3.3 | Benchmarks used for our experiments                                              | 50 |

| 3.4 | Impact of increasing number of inliers                                           | 54 |

| 3.5 | Profiling data for the code with 60 LocalMaxima                                  | 55 |

| 4.1 | Features of the global performance optimization options                          | 58 |

| 4.2 | Average power, execution time, and energy for the investigated benchmarks.       | 67 |

| 4.3 | SIMD effect when no optimization option is invoked                               | 71 |

| 4.4 | Impact of SIMD when -o0 optimization options are invoked                         | 71 |

| 4.5 | SIMD influence when -o1 optimization options are invoked                         | 72 |

| 4.6 | SIMD Impact when -o2-mu (SPLOOP is disabled) optimization options are invoked    | 73 |

| 4.7 | Impact of SIMD when -o3-mu (SPLOOP is disabled) optimization options are invoked | 73 |

| 5.1 | Loop reversal transformation effect on energy and power                          | 83 |

| 5.2 | Examples of expression strength reduction                                        | 84 |

| 5.3 | Loop-based strength reduction transformation impact on power and Energy.         | 85 |

| 5.4 | Loop unswitching transformation impact on energy and power consumption.          | 86 |

| 5.5 | Impact of loop permutation on energy and power consumption                       | 87 |

xx List of Tables

| 5.6  | Impact of loop peeling transformation on energy and power consumption                           | 88  |

|------|-------------------------------------------------------------------------------------------------|-----|

| 5.7  | Loop fusion transformation impact on energy and power consumption                               | 89  |

| 5.8  | Impact of loop peeling then fusion on energy and power consumption                              | 90  |

| 5.9  | Influence of loop normalization then fusion transformations on the energy and power consumption | 91  |

| 5.10 | Impact of loop unrolling transformation on energy and power consumption.                        | 92  |

| 5.11 | Impact of loop tiling transformation on energy and power consumption                            | 94  |

| 5.12 | Influence of array elements scalarization transformation on the energy and power consumption    | 96  |

| 5.13 | Influence of procedure call preprocessing transformations on the energy and power consumption   | 97  |

| 5.14 | Influence of procedure integration transformations on the energy and power consumption          | 99  |

| B.1  | Algorithmic parameters calculation methodology                                                  | 127 |

| B.2  | Complete power consumption model for C6416T DSP at $F=1000 \mathrm{MHz}$                        | 128 |

| B.3  | Power Estimation for different benchmarks at $F=1000 \mathrm{MHz}$                              | 129 |

| C.1  | Pseudonyms for the applications used for PCA                                                    | 137 |

## 1 INTRODUCTION

## 1.1 Embedded Systems

An embedded system is a combination of computer hardware and software and sometimes additional parts, either mechanical or electronical designed to perform a dedicated function. The design of an embedded system to perform a dedicated function is in direct contrast to that of the personal computer. It is also comprised of computer hardware and software and mechanical components (disk drives, for example). However, a personal computer is not designed to perform a specific function. Rather, it is able to do many different things. Many people use the term general-purpose computer to make this distinction clear. As shipped, a general-purpose computer is a blank slate; the manufacturer does not know what the customer will do with it. Frequently, an embedded system is a component within some larger system. For example, modern cars and trucks contain many embedded systems. One embedded system controls the anti-lock brakes, another monitors and controls the vehicle's emissions, and a third displays information on the dashboard. Some luxury car manufacturers have even touted the number of processors (often more than 60, including one in each headlight) in advertisements. In most cases, automotive embedded systems are connected by a communications network [1].

In general, "embedded system" is not an exactly defined term, as many systems have some element of programmability. For example, handheld computers share some elements with embedded systems such as the operating systems and microprocessors which power them but are not truly embedded systems, because they allow different applications to be loaded and peripherals to be connected. Embedded systems exhibit certain characteristics that distinguish them from other computing systems. These characteristics are:

• **Single function:** An embedded system usually executes a certain task (or program) repeatedly.

• **Reactive:** Also called Event-Driven, continually reacts to changes in the systems environment. For example, a car's cruise controller must monitor and react to speed and brake sensors.

- **Real-time:** Must compute certain results in certain time without delay.

- **Tightly-constrained:** Because of the nature of embedded systems, their design metrics such as size, speed and power impose tight constraints.

### 1.1.1 Target Architectures for Embedded Systems

The most typical architectural structures for embedded systems concentrate essentially onto a range of processing units: relevant for software implementations are micro-Controllers ( $\mu$ Cs) and Digital Signal Processors (DSPs), or even more specific Application Specific Instruction-Set Processors (ASIPs), typical candidates for hardware implementation are programmable logic and dedicated data-paths. A mixture of these components is either assembled onto a single chip for which the term System-on-Chip (SoC) has prevailed, or is composed by several chips onto a board system.

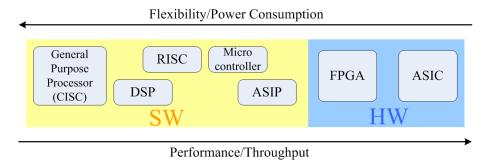

Fig. 1.1: Architectural components and their affiliation to hardware and software.

Figure 1.1 visualizes the common notion of the trade-off between hardware and software architectural components. From the left to the right the complexity of the underlying component is decreasing in terms of instruction set, sophisticated memory access, and pipelining strategies. This is counterbalanced by the increase of the computational speed towards Application Specific Integrated Circuits (ASICs), mostly measured in throughput or number of operations per time unit. The grouping of these processor classes into hardware and software systems has not been clearly defined but is generally understood [2, 3]. In the next paragraphs we present a short overview over the different embedded system architectures.

### 1.1.1.1 General-Purpose Processors

Although General-Purpose Processors (GPPs) are not considered as viable choices in embedded systems, a short description is given to round up the picture. These processor types are all-rounders on which nearly any application can be executed with a medium performance instead of being optimal for just a single one. Workstations, PCs, servers, and much more are typical candidates for a deployment of these processors. The steep requirements on flexibility and processing speed necessitate very complex circuit structures with superpipelining, branch prediction, hierarchical caching structures, and superscalar scheduling by prefetching instructions. The execution time of a characteristic code block varies therefore, as it is dependent on a number of dynamic effects. For real time systems with strict deadlines on certain parts of the functionality, these processors are normally inappropriate. Another obstacle for the deployment of GPPs in embedded systems is the large power consumption and the tedious and time-consuming interface design for I/O and memory access due to the aforementioned circuit complexity.

## 1.1.1.2 Digital Signal Processors

Digital Signal Processors (DSPs) are processors dedicated to a specific application domain of digital signal processing, e.g. mobile communication, image processing, audio/video applications. With respect to the general instruction set, they offer very much the same possibilities as general-purpose processors but with less facets and simpler circuitry. Their big advantage is the optimized circuitry for *additional* instructions catering to the specific application domain. Relevant traits for DSPs are amongst:

- Combined multiply-accumulate (MAC) operations.

- In a single instruction cycle a multiply operation of two operands is interlinked with a subsequent accumulation of the result. This instruction has a direct realization in hardware circuitry in a DSP for floating-point or fixed point number formats.

- High jump predictability and zero-overhead loops.

A humble level of code branching and fixed loop count variable is exploited by special registers, in which start and end address and the loop counter is stored. Every iteration through the loop body triggers the counter's increment or decrement and the subsequent comparison with the end condition, thus not imposing any overhead due to loop

controlling.

• Specialized addressing techniques.

DSPs provide address generators that are capable to increment or decrement the address pointer by a programmable step width in parallel to the actual instruction processing. Two relevant applications are the circular address scheme, which facilitates filter implementations and bit-reverse address schemes for e.g. Walsh-Hadamard or Fast Fourier Transforms.

Many embedded systems comprise DSPs with fixed-point numeric formats, since a fixed-point arithmetic logic unit (ALU) is much faster than a floating-point ALU given the same chip area. However, the transition towards fixed-point formats additionally complicates the design due to quantization noise, rounding and overflow errors.

Nowadays, C-compilers exist for most of the DSPs on the market, but crucial functions may still be designed in assembler to ensure a better exploitation of the specific architectural features of the DSP. For many applications, as in the image processing domain, time critical code parts that have been manually optimized in assembler can be embedded into C routines.

The digital signal processing domain gained significant attention due to the revolution in mobile communications. Therefore, a large variety of different DSP cores emerged with manyfold innovative architectures [4]: for instance multiple DSP platforms, very large instruction word (VLIW) DSPs, and desktop DSPs.

#### 1.1.1.3 Microcontrollers

As the name suggests a micro controller ( $\mu$ C) is dedicated to control flow dominated applications like protocols that are characterized by a large number of branches, internal states, and boolean logic operations. The data throughput as well as the arithmetic operations do not play a major role. Typically,  $\mu$ Cs are used for interrupt handling and support a very fast context switching often seen in protocol state machines. In other words, the current program context is realized completely in the RAM, so that in the case of an interrupt the program address pointer is simply set to a new address.

### 1.1.1.4 Application Specific Instruction Set Processors

These  $\mu$ Ps are even more customized to their specific application domain than DSPs and micro controllers. The key idea is the application-directed generation of a *programmable* device, whose instruction set and data word widths have undergone a fierce optimization towards its purpose. As indicated in Figure 1.1, ASIPs occupy the location with the least flexibility and the highest performance in the software domain.

Since ASIPs are by definition application specific, it is difficult to classify them by their commonalities. Usually, their instruction set includes operator concatenation as MAC operations, or vector arithmetics. Similar to their larger siblings, the DSPs, their circuitry exploits parallelism of address calculation and data operations. On the contrary, ASIPs usually dispense complicated caching schemes and reduce the pin number as far as possible to enable smaller chip sizes. The development of optimizing compilers, debuggers, and linkers for ASIPs has long been subject to intense research. In recent years, a design group from RWTH Aachen developed a mature tool suite for ASIP design called LISA [5,6], which is now commercially available in the portfolio of CoWare [7].

### 1.1.1.5 Field Programmable Gate Arrays

Field programmable gate arrays (FPGA) belong in our notion to the hardware domain, although being programmable as the name suggests. A regular arrangement of configurable logic blocks (CLB) is programmable by adjusting the interconnects between them in order to duplicate basic logic gates as AND, OR, XOR, memory or more complex combinatorial functions. The CLBs contain look-up tables, multiplexers, and flip-flops, whose structure usually differs widely to offer high flexibility on a single FPGA. The interconnection network occupies the major portion of the chip area of up to 90%. I/O blocks surround the CLB grid. It is in general distinguished between one time only programming of FPGAs with anti-fuse switches and reconfigurable programming of FPGAs with SRAM switches. In the first case the interconnects and configuration of the multiplexers are burned onto the die to establish a connection (thus *anti*-fuse).

Eventually, these FPGAs resemble ASICs, as their behavior is permanently determined. The configuration of SRAM based FPGAs is accomplished by setting variables in the SRAM units that determine the interconnects and multiplexers. In modern FPGAs at every power up of the FPGA the configuration is loaded from an EEPROM. The development of FPGA cir-

cuitry resembles very much the development of ASICs. Classical hardware design tools are utilized to develop schematics and netlists of integrated circuit elements (gates, flip-flops). The FPGA vendor usually offers integrated tools for the schematics, which automatically transpose the netlist into the configuration data and eventually configures the FPGA.

### 1.1.2 Embedded Systems Design Metrics

To cope with the rapidly growing complexity of embedded systems, designers must work at higher levels of abstraction [8]. Depending on the abstraction layer, the level of detail used to describe the system, designers can address different concerns. The key is to model the system at each abstraction layer with as little detail as possible and then collect performance metrics that help the development team make sound engineering decisions.

Among the many metrics used to characterize the quality of an embedded system design, we will go through the following metrics:

- Execution-time

- Non-Recurring Engineering (NRE)

- Flexibility

- Time-to-Market

- Power consumption

- Size

- Unit cost

- Maintainability

**Execution-time:** (as a measure of the embedded system performance) plays an important role in the area of embedded systems and especially hard constrained real-time systems. These systems are typically subject to stringent timing constraints, which often result from the interaction with the surrounding physical environment. It is essential that the computations are completed within their associated time bounds; otherwise severe damages may result, or the system may be unusable. Therefore, a schedulability analysis has to be performed which guarantees that all timing constraints will be met. Schedulability analysis requires the upper bounds for the execution times of all tasks in the system to be known. These bounds must be safe, that is, they may never underestimate the real execution time. Furthermore, they should be tight, that is, the overestimation should be as small as possible. In modern microprocessor architectures, caches, pipelines, and all kinds of speculation are key features for improving (average-case) performance. Unfortunately, they make the analysis of the timing behavior of instructions very difficult, since the execution time of an instruction depends on the execution history. A lack of precision in the predicted timing behavior may lead to a waste of hardware resources, which would have to be invested in order to meet the requirements [9].

**Power consumption:** has emerged as one of the most important embedded systems design metrics. This is largely due to the proliferation of mobile battery-powered computing devices, the increasing speed and density of CMOS (complementary metal-oxide semiconductor) VLSI (very large-scale integration) circuits, and continuous shrinking of the transistor feature size of deep sub-micron technologies [10].

Power consumption is a major concern for portable or battery-operated devices. Power issues, such as how long the device needs to run and whether the batteries can be recharged, need to be thought out ahead of time. In some systems, replacing a battery in a device can be a big expense. This means the system must be conscious of the amount of power it uses and take appropriate steps to conserve battery life. There are several methods to conserve power in an embedded system, including clock control, power-sensitive processors, low-voltage ICs, and circuit shutdown. Some of these techniques must be addressed by the hardware designer in his selection of the different system ICs. Some power-saving techniques are under software control.

It might seem ideal to select the fastest and most powerful processor available for a particular embedded system. However, one of the tasks of the hardware designer is to use just enough processing power to enable the device to get its job done. This helps reducing the power consumed by the device. The selected processor plays a key role in determining the amount of power an embedded system will consume. In addition, some processors can automatically shut down different execution units when they are not in use [1].

One software technique offered by many embedded processors to conserve power is different operating modes (e.g. run, idle and sleep). These modes allow the software to scale processor power consumption to match the moment-by-moment needs of the application. Operating the processor in different modes can save quite a bit of power. Another power-saving technique that can be controlled by software is to vary processor clock speeds. Some processors accept a fixed-input clock frequency but feature the ability to reduce internal clock speeds by programming clock configuration registers. Software can reduce the clock speed to save power during the execution of noncritical tasks and increase the clock speed when processing demands are high. Substantial power/energy savings can also be achieved through the implementation of adequate dynamic power management policies, for example, tracking instantaneous workloads (or levels of resource utilization) and shutting-down idling/unused resources, so as to reduce leakage power, or slowing down under-utilized re-

sources, so as to decrease dynamic power dissipation [1,9].

**Non-Recurring Engineering (NRE):** refers to the one-time cost of researching, developing, designing, and testing a new product. When budgeting for a project, NRE must be considered in order to analyze if a new product will be profitable. Even though a company will pay for NRE on a project only once, NRE can be considerably high and the product will have to sell well enough to produce a return on the initial investment. NRE is unlike production cost, which must be paid continually in order to maintain production.

In a project-type company, large parts (possibly all) of the project represent NRE. In this case the NRE cost are likely be included in the first project's cost. If the company cannot recover this cost, it will have to consider funding part of these from reserves (possibly make a project loss) in the hope that the investment can be recovered from additional profit on future projects [11].

*Size:* the physical space required by the system, e.g., bytes of memory for software and logic gates or Configurable Logic Blocks (CLB) for hardware.

*Flexibility:* the ability to change the functionality of the system without incurring heavy NRE cost.

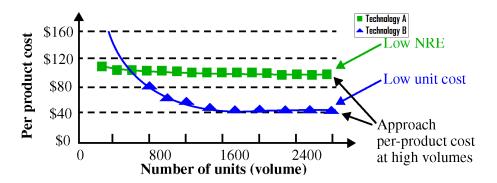

*Unit cost:* the monetary cost of manufacturing each copy of the system, excluding NRE cost. When comparing technologies by cost, the best option depends on quantity. Let's assume that there are two alternatives technologies for a certain product. The first alternative is technology A; which has a NRE cost of \$2 000 and a unit cost of \$100. The second alternative technology B with a NRE cost of \$30 000 and a unit cost of \$30. Figure 1.2 illustrates the strong impact of the NRE and the production volume on the final product unit cost [12].

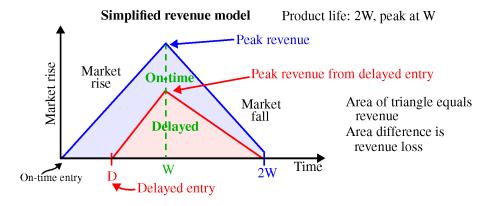

*Time-to-Market:* the time required to develop a system to the point that it can be released and sold to customers. Growing system complexities, driven by increased IC capacities, requires designers to do more in less time. Figure 1.3 indicates the importance of the time-to-market design metrics from the revenue point of view.

Delays can be costly. Equation (1.1) expresses the percentage of revenue lost. Assume that market rise in Fig. 1.3 is at 45 degree angle and that the product life is 2W with a peak market rise at W. Hence (1.2) and (1.3) define the on-time and delayed design entry point for the product. By substituting in (1.1) the final revenue model in (1.4) is obtained. For

Fig. 1.2: NRE and production volume influence on the product unit cost (reproduced from [12]).

Fig. 1.3: Time-to-Market design metrics impact on the market revenue (reproduced from [12]).

example let 2W=52 weeks, delay D=10 weeks hence, by substituting in (1.4) we find out that the percentage revenue lost due to 10 weeks delay in the entry to the market equals 50% [12].

% revenue lost =

$$\frac{\text{revenue}_{\text{On-time}} - \text{revenue}_{\text{Delayed}}}{\text{revenue}_{\text{On-time}}} \times 100$$

(1.1)

$$revenue_{On-time} = \frac{1}{2} \times 2W \times W = W^2, \tag{1.2}$$

$$revenue_{Delayed} = \frac{1}{2} \times (W - D + W) \times (W - D), \tag{1.3}$$

% revenue lost =

$$\frac{D(3W - D)}{2W^2} \times 100$$

(1.4)

Maintainability: measures the ease and speed with which a system can be restored to oper-

ational status after a failure occurs [12–14].

## 1.2 Motivation

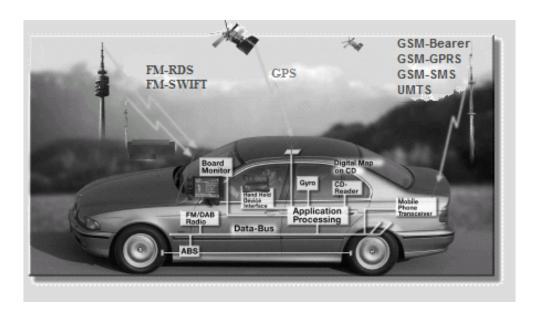

Embedded systems are rapidly growing in the few recent years. As shown in Fig. 1.4 more than 30% of the car is now in electronics and almost 90% of innovations will be based on electronics [14]. As illustrated in the previous section, the power and energy constraints on embedded systems are becoming increasingly tight as complexity and performance requirements continue to be pushed by the user demand [15].

Fig. 1.4: Embedded systems in automotive electronics (reproduced from [14]).

Power density has a direct impact on packaging and cooling cost, and can also affect system reliability, owing to electromigration [16] and hot-electron [17] degradation effects. Thus, the ability to decrease power density, while offering similar performance and functionality, critically enhances the competitiveness of a product. Moreover, for battery operated portable systems, maximizing battery lifetime translates into maximizing duration of service, an objective of paramount importance for this class of products. Power is thus a primary figure of merit in contemporary embedded system design [9].

Integrated circuits in their various manifestations consume some amount of electric power. This power is dissipated both by the action of the switching devices contained in IC (such as transistors) as well as heat due to the resistivity of the electrical circuits. This is a major

1.3. Contributions

consideration in the design of micro-processors and the embedded systems they are utilized in.

Today, digital signal processors (DSPs) are frequently used in embedded systems to permit application specifications in software. Processor speeds have doubled approximately every 18 months as predicted by Moore's law [18]. In order to get an energy-efficient system consisting of processor and compiler, it is necessary to optimize hardware as well as software [19].

The program behavior is difficult to predict due to its heavy dependence on application and run-time conditions [20,21]. For embedded systems, the application performance can be optimized by utilizing parallel hardware architectures, such as Very-Long Instruction Word (VLIW) architectures [6]. VLIW architectures are a suitable alternative for exploiting Instruction-Level Parallelism (ILP) in programs, that is, for executing more than one basic (primitive) instruction at a time. These processors contain multiple functional units. They fetch from the instruction cache a VLIW containing several primitive instructions, and dispatch the entire VLIW for parallel execution.

These capabilities are exploited by compilers which generate code that has grouped together independent primitive instructions executable in parallel. The processors have a relatively simple control logic because they do not perform any dynamic scheduling nor reordering of operations (as is the case in most contemporary superscalar processors). The instruction set for a VLIW architecture tends to consist of simple instructions (RISC-like). The compiler must assemble many primitive operations into a single instruction word such that the multiple functional units are kept busy, which requires enough ILP in a code sequence to fill the available operation slots.

#### 1.3 Contributions

The main contributions of this dissertation can be summarized in the following folds:

- First, a complete power and energy characterization of the VLIW fixed-point C6416T DSP is performed.

- The first step toward this power characterization is the design and implementation of a precise high level software power consumption model for the targeted

processor, while running a software algorithm.

Next, we prove the validation and precision of our model on many typical algorithms applied in signal and image processing.

- The power consumption estimated by our model, is compared to the physically measured power consumption, achieving a very low average estimation error of 1.65% and a maximum estimation error of only 3.3%

- 2. Second, a quantitative study is provided wherein we examine the influence of the global optimizations of the C/C++ compiler, of the code composer studio, with respect to the energy and power consumption.

- we find that enabling general compiler performance optimizations considerably increase the power consumption of the DSP, on average, by 30.35% when the third optimization level (-o3) is invoked.

- In order to analyze the causes for the power increase we study the effect on some other performance measures, such as:

• L1D cache misses

- Instructions per cycle

- Memory references

- CPU stall cycles

- The impact of the special C64x+ architecture feature; namely Software Pipelined Loop (SPLOOP) on the energy usage and power consumption is evaluated.

- Moreover, the impact of utilizing the targeted architecture Single Instruction Multiple Data (SIMD) capabilities on the energy usage and power consumption is evaluated.

- Finally, the characterization of the application-architecture correlation for the targeted platform. The Pricipal Component Analysis (PCA) multivariate statistical technique is employed to visualize the black box impact of the compiler and the hardware architecture over the software applications. This is achieved with the aid of biplots which is depicted in our analysis in such a way, so that it can show the maximum association between the application and the underlying hardware architecture. Hence, it answers the question whether a given hardware architecture is an appropriate choice for a given software application or not.

- 3. Third, since the CCS allows very limited control over the individual optimization tasks embedded within each global optimization levels, we assess the effect of applying source to source code transformations on the power, energy and performance. The

1.4. Thesis Outline

source code transformations that are presented in this work are classified into three major groups: loop, data and procedural transformations.

This thesis is based on the following publications:

- Mostafa E. A. Ibrahim, Markus Rupp, and S. E.-D. Habib. Power consumption model at functional level for VLIW digital signal processor. In proceedings of the conference on Design and Architectures for Signal and Image Processing (DASIP'08), Bruxelle, Belgium, pages 147-152, November 2008.

- Mostafa E. A. Ibrahim, Markus Rupp, and Hossam A. H. Fahmy. Power Estimation Methodology for VLIW Digital Signal Processor. In proceedings of the IEEE conference on Signals, Systems and Computers (SSC'08), Asilomar, CA, US, IEEE, pages 1840-1844, October 2008.

- Mostafa E. A. Ibrahim, Markus Rupp, and S. E.-D. Habib. Compiler-Based Optimizations Impact on Embedded Software Power Consumption. In proceedings of the joint IEEE conference NEWCAS-TAISA'09 Toulouse, France, pages 247-250, June 2009.

- Mostafa E. A. Ibrahim, Markus Rupp, and S. E.-D. Habib. Performance and Power Consumption Trade-offs for a VLIW DSP. In proceedings of the IEEE International Symposium on Signals, Circuits and Systems (ISSCS'09), Iasi, Romania, pages 197-200, July 2009.

- Mostafa E. A. Ibrahim, Markus Rupp, and Hossam A. H. Fahmy. Impact of Code Transformations and SIMD on Embedded Software Power Consumption. In proceedings of the IEEE International Conference on Computer Engineering and Systems (ICCES'09), Cairo, Egypt, December 2009.

#### 1.4 Thesis Outline

The rest of this thesis is structured as follows:

Chapter 2 reviews the evolution and state-of-the-art in processor's power consumption models that rely on the running software. In general two main abstraction levels are surveyed in this chapter. The low-level power modeling and estimation techniques cover the circuit-level, gate-level, Register Transfer (RT)-level and the micro-architecture level. The high-level techniques can be divided into two categories the Instruction Level Power Analysis

(ILPA) and the Functional Level Power Analysis (FLPA). The software and hardware based power saving techniques are surveyed, focusing on the recent attempts to evaluate the impact of different compiler optimizations on the energy and power consumption of the processor. The variety of existing source to source code transformations are analyzed from power and energy perspectives .

Chapter 3 proposes a precise model to estimate the power consumption of the targeted DSP, while running a software algorithm. The modeling is performed at the functional level making this approach distinctly different from other modeling approaches in low level techniques. This means that the power consumption can be identified at an early stage in the design process, enabling the designer to explore different hardware architectures and algorithms. After applying the FLPA, the targeted C6416T architecture is subdivided into six distinct functional blocks (clock tree, instruction management unit, processing unit, internal memory, L1 data cache and L1 program cache). The parameters that affect the power consumption for the identified functional blocks are determined. Typical signal and image processing algorithms and a real time application are used for the purpose of validating the proposed model. The estimated power consumption is compared to the physically measured power consumption

Chapter 4 explores the performance and power trade-offs of the VLIW Texas Instruments C6416T DSP. We assess the effect of the compiler performance optimizations on the energy and power consumption. Moreover, we explore the impact of two special architectural features of this DSP; namely Software Pipelined Loop (SPLOOP) and the SIMD capabilities, on the energy and power consumption. The code binaries utilized in this study were generated with aid of the Texas Instrument C/C++ Compiler that is embedded in the CCS, which allows control over the whole set of optimizations. Finally, we explore the correlation between the software applications and the underlying hardware architecture at which these applications are executed. We employ the Principal Component Analysis (PCA) biplots to visualize the black box impact of compiler and hardware architecture over the software applications.

**Chapter 5** assesses the effect of applying source to source code transformations on the power, energy and performance. The source code transformations that are presented in this work are classified into three major groups: data oriented transformations, loop oriented

1.4. Thesis Outline

transformations and finally procedural and inter-procedural transformations. To evaluate the effectiveness of the applied transformations we compile each program, both the original and transformed version, on the target architecture (C6416T DSK). Next, we record the current drawn from the core CPU and hence the consumed power. With the aid of the compiler's profiler we also record the run time and other execution characteristics such as memory references, L1D cache misses and so on. To obtain reliable and precise information, we repeat the whole measuring procedure for each transformation multiple times.

**Chapter 6** concludes the thesis commenting on the probable impact of the obtained results. In addition to the summary of the presented unique contributions, a discussion of the possible future directions of research based on this thesis is presented.

**Appendix A** illustrates an overview of the DSP products of Texas Instrument Inc., the market leader in DSP field, focusing on the architecture of our target DSP C6416T. Moreover this appendix lists the C6416T simulator's performance monitoring events along with their description.

**Appendix B** shows how the algorithmic parameters, required to estimate the power consumption of the running algorithm, are computed. In addition, it shows the actual computed parameters, the estimated, the measured power consumption for different image and signal processing benchmarks and finally a complete power consumption model at an operating frequency of 1 000MHz.

**Appendix** C explains some basic foundations regarding the multivariate statistical technique named Principal Component Analysis (PCA) which is used to characterize the application-architecture correlation.

**Appendix D** lists the different acronyms utilized in this thesis.

# 2 RELATED WORK

#### 2.1 Introduction

In this chapter we review the evolution and state-of-the-art in processor's power consumption models that rely on the running software. In general two main abstraction levels are surveyed in this chapter. The low-level power modeling and estimation techniques cover the circuit-level, gate-level, Register Transfer (RT)-level and the micro-architecture level. The high-level techniques can be divided into two categories the Instruction Level Power Analysis (ILPA) and the Functional Level Power Analysis (FLPA). We also survey the software and hardware based power saving techniques, focusing on the recent attempts to evaluate the impact of invoking different compiler optimization levels on the energy and power consumption of the processor. Finally, we analyze the variety of existing source to source code transformations from power and energy perspectives.

# 2.2 Software Power Consumption Estimation Techniques

This section summarizes the most recent contributions to the problem of power modeling and estimation. Recent approaches to model the power consumption of the software running on a processor can be separated into two main categories:

- Low-Level or Hardware level models.

- High-Level models.

Hardware level models calculate power and energy from detailed electrical descriptions, comprising circuit level, gate level, register transfer (RT) level or system level. High-Level models deal only with instructions and functional units from the software point of view and without electrical knowledge of the underlying architecture [22].

#### 2.2.1 Low-Level Estimation Techniques

The level of detail in the modeling performed by the power simulator influences both the accuracy of estimation as well as the speed of the simulator. In this section we survey the frequently used models at low level. The low level power consumption estimation techniques cover a range of abstractions such as the:

- Circuit/Transistor level.

- Logic gate level.

- RT-level.

- Architectural level.

#### 2.2.1.1 Transistor-Level Estimations

The representation of a microprocessor in terms of transistors and nets is extremely complex and requires to undergo all the steps of the design flow and the layout, routing and parameter extraction inclusive. This is rarely feasible since only few big companies have the knowhow and the technology in-house while most of them rely on silicon vendors for the lowest-level steps. Furthermore, a transistor-level view of the system uses components models based on linearized differential equations and works in the continuous time domain. This implies that a simulation of more than one million transistors, even for few clock cycles, requires times that are usually not affordable and anyway not practical for the high-level power characterization [23].

The PowerMil [24] is an early attempt to build a low-level power consumption simulator. PowerMil is a transistor level simulator for simulating the current and power behavior in VLSI circuits. It is capable of simulating detailed current behavior in modern deep submicron CMOS circuits, including sophisticated circuitries such as sense-amplifiers, with speed and capacity approaching conventional gate level simulators. For more details about power estimation techniques in VLSI circuits refer to [25, 26].

#### 2.2.1.2 Gate-Level Estimations

Methods to estimate the power consumption based on gate-level descriptions of microprocessors or micro controller cores have been proposed in literature. The main advantage of such methods with respect to transistor-level simulation approaches is that the simulation is event-driven and takes place in a discrete time domain, leading to a considerable reduction of the computational complexity, without a significant loss of accuracy [23].

An example for the gate-level power estimators is the model presented by Chou [27]. Chou et al. present an accurate estimation of signal activity at the internal nodes of sequential logic circuits. The power consumption estimation in Chou et al. is a Monte Carlo based approach that take spatial and temporal correlations of logic signals into consideration.

#### 2.2.1.3 RT-Level Estimations

A design described at RT-level can be seen as a collection of blocks and a network of interconnections. The blocks, sometimes referred to as macros, are adders, registers, multiplexers and so on, while the interconnections are simply nets or group of nets. An assumption underlying the great majority of the approaches presented in literature is that the power properties of a block can be derived from an analysis of the block isolated from a design, under controlled operating conditions. The main factor influencing the power consumption model of a macro is the input statistics [23].

Most of the research in RT-level power estimation is based on empirical methods that measure the power consumption of existing implementations and produce models from those measurements. This is in contrast to approaches that rely on information-theoretic measures of activity to estimate power [28, 29]. Measurement-based approaches for estimating the power consumption of datapath functional units can be divided into two sub-categories. The first technique, introduced by Powel and Chau [30], is a fixed-activity micro-modeling strategy called the Power Factor Approximation (PFA) method. The power models are parameterized in terms of complexity parameters and a PFA proportional constant. Similar schemes were also proposed by Kumar et al. [31] and Liu and Svensson [32]. This approach assumes that the inputs do not affect the switching activity of a hardware block. To remedy this problem, activity-sensitive empirical power models were developed. These schemes are

based on predictable input signal statistics; an example is the method proposed by Landman and Rabaey [33]. Although the individual models built in this way are relatively accurate (a 10% - 15% error rate), overall accuracy may be negatively affected due to incorrect input statistics or the inability to correctly model the interaction.

The second empirical technique, transition-sensitive power models, is based on input transitions rather than input statistics. The method, proposed by Mehta, Irwin, and Owens [34], assumes a power model is provided for each functional unit- a table containing the power consumed for each input transition. Closely related input transitions and power patterns can be concentrated in to clusters, thereby reducing the size of the table. Other researchers have also proposed similar macro-model based power estimation approaches [35, 36].

#### 2.2.1.4 Architectural-Level Estimations

Recently, various architectural power simulators have been designed that employ a combination of lower level of abstraction power consumption models. These simulators derive power estimates from the analysis of circuit activity induced by the application programmes during each cycle and from detailed capacitive models for the components activated. A key distinction between these different simulators is in the degree of estimation accuracy and estimation speed. For example, the *SimplePower* power simulator [37] employs a transition-sensitive power model for the datapath functional unit. The *SimplePower* core accesses a table containing the switch capacitance for each input transition of the functional unit exercised.

The use of a transition-sensitive approach has both design challenges as well as performance concerns during simulation. *The first concern* is that the construction of these tables is time consuming. Unfortunately, the size of this table grows exponentially with the size of the inputs. The table construction problem can be addressed by partitioning and clustering mechanisms. Further, not all tables grow exponentially with the number of inputs. For example, consider a bit-independent functional unit such as a pipeline register where the operation of each bit slice does not depend on the values of other bit slices. In this case, the only switch capacitance table needed is a small table for a one-bit slice. The total power consumed by the module can be calculated by summing the power consumed by each bit transition.

A second concern with employing transition-sensitive models is the performance cost of the table lookup for each component access in a cycle. In order to overcome this cost, simulators such as SoftWatt [38] and Wattch [39] use a simple fixed-activity model for the functional unit. These simulators only track the number of accesses to a specific component and utilize an average capacity value to estimate the power consumed. Even the same simulator can employ different types of power models for different components. For example, SimplePower estimates the power consumed in the memories utilizing analytical models [40]. In contrast to the datapath components that utilize a transition-sensitive approach, these models estimate the power consumed per access and do not accommodate the power differences found in sequences of accesses.

One of the most widely used micro-architectural power simulators is *Wattch* [39]. *Wattch* is a power simulator for superscalar, out-of-order, processors. It has been developed with aid of the infrastructure offered by *SimpleScaler* [41]. *SimpleScaler* performs fast, flexible, and accurate simulation of modern processors that implement a derivative of the MIPS-IV architecture and support superscalar, out-of-order, execution. The power estimation engine of *Wattch* is based on the *SimpleScaler* architecture, but in addition, it supports detailed cycle-accurate information for all models, including datapath elements, memory and Content Addressable Memory(CAM) arrays, control logic, and clock distribution network. *Wattch* uses activity-driven, parameterizable power models, and it displayed an accuracy better than 10% when tested on three different architectures. Another approach to evaluate energy estimates at the architectural-level exploits the correlation between performance and energy metrics. These techniques [42, 43] use performance counters present in many current processors architectures to provide runtime energy estimates [44].

While providing excellent accuracy; low-level power estimation methodologies are slow and impractical for analyzing the power consumption at an early design stage. Moreover, these methodologies require the availability of lower level circuit details or a complete Hardware Description Language (HDL) design of the targeted processor, which is not available for most of commercial off-the-shelf processors.

#### 2.2.2 High-Level Estimation Techniques

Recently, the demand increased for high level power estimation simulators that allow an early design space exploration from the power consumption perspective. The existing high-level power estimation models can be classified into two main categories, Instruction Level Power Analysis (ILPA) and Functional Level Power Analysis (FLPA).

#### 2.2.2.1 Instruction Level Power Analysis

An instruction level power model for individual processors was first proposed by V. Tiwari et al. [45]. By measuring the current drawn by the processor as it repeatedly executes distinct instructions or distinct instruction sequences, it is possible to obtain most of the information that is required to evaluate the power consumption of a program for the processor under test. V. Tiwari et al. modeled the power consumption of the Intel DX486 processor. Power is modeled as a base cost for each instruction plus the inter-instruction overheads that depend on neighboring instructions. The base cost of an instruction can be considered as the cost associated with the basic processing needed to execute the instruction. However, when sequences of instructions are considered, certain inter-instruction effects come into play, which are not reflected in the cost computed solely from base cost. These effects can be summarized as:

- Circuit state: switching activity depends on the current inputs and previous circuit state. In other words the difference between the bit pattern of two successive instructions.

- Resource Constraints: Resource constraints in the CPU can lead to stalls e.g. pipeline stalls and write buffer stalls.

- Cache Misses: Another inter-instruction effect is the effect of cache misses. The instruction timings listed in manuals give the cycle count assuming a cache hit. For a cache miss, a certain cycle penalty has to be added to the instruction execution time.

An experimental method is proposed by V. Tiwari et al. to empirically determine the base and the inter-instructions overhead cost. In this experimental method, several programs containing an infinite loop consisting of several instances of the given instruction or instruction sequences are used. The average current drawn by the processor core during the execution of this loop is measured by a standard off-the-shelf, dual-slope integrating digital multi-meter as shown in Fig. 2.1.

Fig. 2.1: Experimental Setup used for current measurements in [45].

Much more accurate measuring environments have been proposed to precisely monitor the instantaneous current drawn by the processor instead of the average current. One of these approaches has used a high-performance current mirror, based on bipolar junction transistors as current sensing circuit as shown in Fig. 2.2. The power profiler in Niloladies et al. [46] receives as input the trace file of executed assembly instructions, generated by an appropriate processor simulator, and estimates the base and inter-instruction energy cost of the executed program taking into account the energy sensitive factors as well as the effect of pipeline stalls and flushes. The main disadvantage of this approach is the current measuring complexity. [47].

Another approach, to reduce the spatial complexity of instruction-level power models, is presented in [48]. Therein, inter-instruction effects have been measured by considering only the additional energy consumption observed when a generic instruction is executed after a No-Operation (NOP) instruction.

An attempt to modify the original ILPA to create an instruction level power model with a gate level simulator is carried out by Sama et al. [49]. In this approach, the power cost values were obtained through a power simulator rather than actual measurement; thus modeling is possible at design time and can be part of micro-architecture and/or instruction set architecture exploration. More researchers attempted to enhance the original Tiwari ILPA power

Fig. 2.2: (a) Experimental Setup for current measurement, (b) The simple current mirror. DUT is the Device Under Test [46].

consumption modeling technique as in [50–52].

The ILPA based methods have some drawbacks, one of these drawbacks is that the number of current measurements is directly related to the number of instructions in the Instruction Set Architecture (ISA), and also the number of parallel instructions composing the very long instruction in the VLIW processor. The problem of instruction level power characterization of K-issue VLIW processor is  $O(N^{2K})$  where N is the number of instructions in the ISA and K is number of parallel instructions composing the VLIW [53]. Also they do not provide any insight on the instantaneous causes of power consumption within the processor core, which is seen as a black-box model. Moreover, the effect of varying data (as well as address) is ignored in the ILPA models, though this effect can be accounted by an additive factor [54].

# 2.2.2.2 Function Level Power Analysis

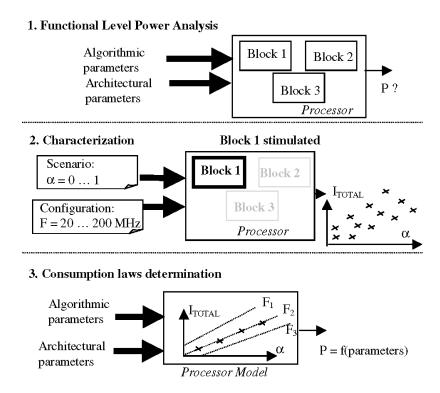

FLPA was first introduced by J. Laurent et al. in [55]. Figure 2.3 illustrates the process of estimating the power consumption with aid of the FLPA technique. The basic idea behind the FLPA is the distinction of the processor architecture into functional blocks like Processing Unit (PU), Instruction Management Unit (IMU), internal memory and others [55]. First, a functional analysis of these blocks is performed to specify and then discard the nonconsuming blocks (those with negligible impact on the power consumption). The second step is to figure out the parameters that affect the power consumption of each of the power consuming blocks. For instance, the IMU is affected by the instructions dispatching rate