# BINARY FLOATING POINT ARITHMETIC VERIFICATION USING A STANDARD LANGUAGE TO SOLVE CONSTRAINTS

By

# Khaled Mohamed Abdel Maksoud Nouh

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in ELECTRONICS AND COMMUNICATION ENGINEERING

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2016

# BINARY FLOATING POINT ARITHMETIC VERIFICATION USING A STANDARD LANGUAGE TO SOLVE CONSTRAINTS

By Khaled Mohamed Abdel Maksoud Nouh

A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in ELECTRONICS AND COMMUNICATION ENGINEERING

Under the Supervision of

Prof. Dr. Hossam A. H. Fahmy

Electronics and Communication Department Faculty of Engineering, Cairo University

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2016

# BINARY FLOATING POINT ARITHMETIC VERIFICATION USING A STANDARD LANGUAGE TO SOLVE CONSTRAINTS

By Khaled Mohamed Abdel Maksoud Nouh

## A Thesis Submitted to the Faculty of Engineering at Cairo University in Partial Fulfillment of the Requirements for the Degree of MASTER OF SCIENCE in

## ELECTRONICS AND COMMUNICATION ENGINEERING

Approved by the Examining Committee

Prof. Dr. Hossam A. H. Fahmy, Thesis Main Advisor

Prof. Dr. Ibrahim Mohamed Qamar, Internal Examiner

Prof. Dr. Ashraf M. Salem, External Examiner, Faculty of Engineering, Ain Shams University

## FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2016

| Engineer's Name:          | Khaled Mohamed AbdelMaksoud Nouh         |                                         |

|---------------------------|------------------------------------------|-----------------------------------------|

| Date of Birth:            | 20/7/1987                                |                                         |

| Nationality:              | Egyptian                                 |                                         |

| E-mail:                   | Khaled_nouh@mentor.com                   | desartant                               |

| Phone:                    | 01271110627                              | 12                                      |

| Address:                  | 136, El Narges 4, New cairo              |                                         |

| <b>Registration Date:</b> | 01/10/2010                               |                                         |

| Awarding Date:            | 2016                                     | ( I I I I I I I I I I I I I I I I I I I |

| Degree:                   | Master of Science                        |                                         |

| Department:               | ELECTRONICS AND COMMUNICAT               | TION                                    |

| -                         | ENGINEERING                              |                                         |

| Supervisors:              |                                          |                                         |

| Supervisers               | Prof. Dr. Hossam A. H. Fahmy             |                                         |

| Examiners:                |                                          |                                         |

| Examiners:                | Prof. Dr. Hossam A. H. Fahmy             |                                         |

|                           | Prof. Dr. Ibrahim Mohamed Qamar          |                                         |

|                           | Prof. Dr. Ashraf M. Salem, Faculty of Er | ngineering Ain                          |

|                           | Shams University                         | ngmeering, Aill                         |

|                           | Shams Oniversity                         |                                         |

#### **Title of Thesis:**

Binary Floating Point Arithmetic Verification using a Standard Language to Solve Constraints

#### **Key Words:**

Floating point arithmetic; Constrained Simulation

#### **Summary:**

Verification of Floating Point (FP) units is a difficult task to achieve, and the cost of post-production bugs is severe. This is due to dealing with a large bit stream of inputs; simulation based verification fails to cover all possible input combinations and hence does not guarantee a 100% bug free design. On the other hand, formal methods are efficient in verification of FP arithmetic, yet they require creating a formal model, they cannot work on an optimized version of a design and may fail with complex designs due to state space explosion.

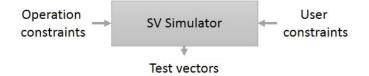

Our framework provides a new verification methodology that uses a constraint based random technique to generate test vectors for validating binary FP arithmetic instructions. The constraints used in our verification are written in System Verilog (SV) language and can be solved with any SV constraint solver tool. For every arithmetic operation, the written constraints couple the operands, intermediate results, rounding direction and the result evaluation to comply with the FP IEEE Standard (IEEE Std 754-2008).

The new proposal is generic and can be used to verify any software or hardware binary FP design/library. Also, it proves feasibility and usefulness in finding bugs for various binary FP Arithmetic operations for single and double precision formats.

# Acknowledgments

First of all, I would like to thank God for giving me the strength and perseverance to complete this research. His greatest gifts are for sure the ladies that light my life, my mother who always pushed me beyond my limits, my wife who held my hands through this tough journey, my late grandmother who guided me with her heavenly blessings and my little girl who represents the future with all what it holds ahead.

Perhaps, having an idol to look up to is one of the biggest motives to excel in work. I was blessed with two: my grandfather, this great man who started from the scratch and reached greatness by means of hard work and self-confidence, he always used to say the "great ones are those with the great deeds", and my father the most knowledgeable person who I always look up to and seek advice from.

I would like also to express my gratitude to my advisor Prof. Hossam Aly Fahmy for his continuous support, guidance and patience. I could not have imagined having a better advisor and mentor.

Last but not the least, I would like to thank my elder brother, my friends and my second family at work, specially my partner in the journey Ahmed Ismail.

# **Table of Contents**

| ACKNOW       | LEDGMENTS                                                                             | I    |

|--------------|---------------------------------------------------------------------------------------|------|

| TABLE O      | F CONTENTS                                                                            | II   |

| LIST OF 1    | TABLES                                                                                | V    |

| LIST OF F    | IGURES                                                                                | VI   |

| ABSTRAC      | Т                                                                                     | VIII |

| СНАРТЕБ      | R 1 : INTRODUCTION                                                                    | 1    |

| 1.1.         | FLOATING POINT NUMBERS                                                                |      |

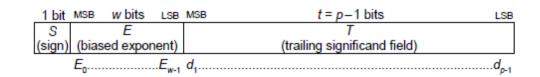

| 1.2.         | IEEE-754 REPRESENTATION OF FLOATING POINT NUMBERS                                     |      |

| 1.2.1.       | Floating point formats                                                                |      |

| 1.2.1.1      | 1. Binary floating point format                                                       |      |

| 1.2.2.       | Floating point arithmetic                                                             | 5    |

|              | 1. Arithmetic operations with operands as infinities and NaNs                         |      |

| 1.2.3.       | Rounding                                                                              |      |

| 1.2.4.       | Exception handling                                                                    |      |

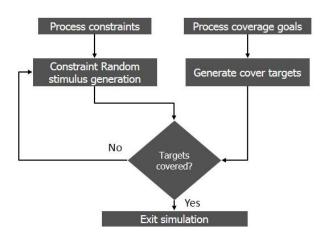

| 1.3.         | RANDOM SIMULATION                                                                     |      |

| 1.3.1.       | Constraint Random Test Pattern Generation                                             |      |

| 1.3.2.       | System Verilog Constraints                                                            |      |

|              | 1. Random Variables in System Verilog                                                 |      |

|              | <ol> <li>Constraint Blocks in system Verilog</li> <li>Randomization method</li> </ol> |      |

| 1.4.         | FLOATING POINT VERIFICATION CHALLENGES                                                |      |

| 1.4.1.       | Wide input.                                                                           |      |

| 1.4.2.       | Usually pipelined implementation                                                      |      |

| 1.4.3.       | No generic solution for Software/Hardware implementation                              |      |

| 1.4.4.       | Dealing with intermediate value before rounding                                       |      |

| 1.5.         | Our verification framework                                                            |      |

| 1.6.         | ORGANIZATION OF THE THESIS                                                            |      |

|              | R 2 : LITERATURE REVIEW                                                               |      |

| 2.1.         | INTRODUCTION                                                                          |      |

| 2.2.         | FORMAL VERIFICATION OF FLOATING POINT ARITHMETIC                                      |      |

| 2.2.         | SIMULATION VERIFICATION OF FLOATING POINT ARTHMETIC                                   |      |

| 2.3.<br>2.4. |                                                                                       |      |

|              | HYBRID TECHNIQUES OF FLOATING POINT VERIFICATION                                      |      |

| 2.5.         | SUMMARY                                                                               |      |

| CHAPTER      | R 3 : PROPOSAL                                                                        | 25   |

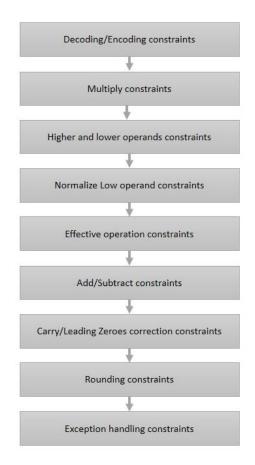

| 3.1.         | ADDITION AND SUBTRACTION                                                              |      |

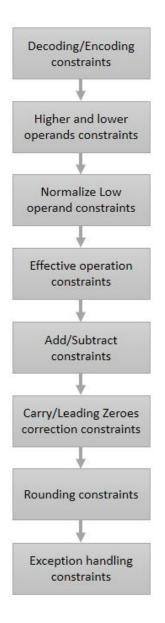

| 3.1.1.       | Encoding/decoding constraints                                                         |      |

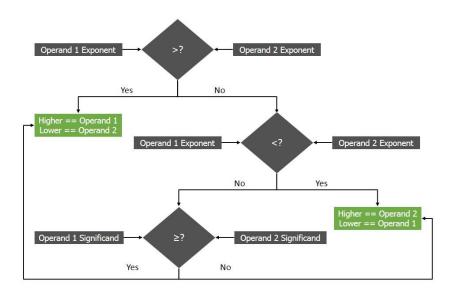

| 3.1.2.       | Higher and lower operands constraints                                                 |      |

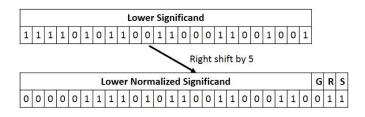

| 3.1.3.       | Normalize low operand constraints                                                     |      |

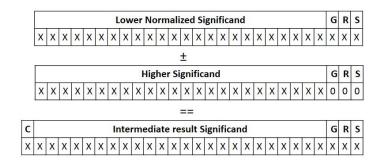

| 3.1.4.       | Effective operation constraints                                                       |      |

| 3.1.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Add/Subtract constraints                                                                                                                                                                                                                                                                                                                                                                                                                 | . 29                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry/Leading Zero correction constraint                                                                                                                                                                                                                                                                                                                                                                                                 | . 30                                                                                                                                             |

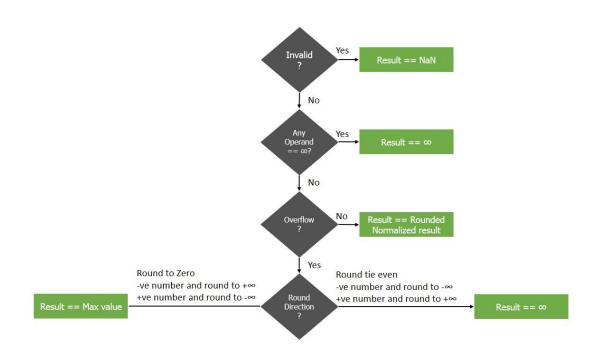

| 3.1.7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rounding constraints                                                                                                                                                                                                                                                                                                                                                                                                                     | . 31                                                                                                                                             |

| 3.1.8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Exception handling constraints                                                                                                                                                                                                                                                                                                                                                                                                           | . 33                                                                                                                                             |

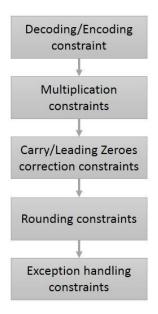

| 3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MULTIPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                           | .34                                                                                                                                              |

| 3.2.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Multiplication constraints                                                                                                                                                                                                                                                                                                                                                                                                               | . 35                                                                                                                                             |

| 3.2.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry/leading Zeroes correction constraints                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                  |

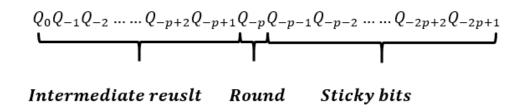

| 3.2.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Rounding constraints                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |

| 3.2.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Exception handling constraints                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                  |

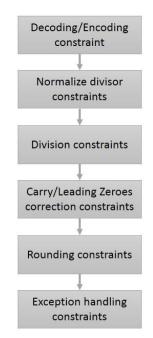

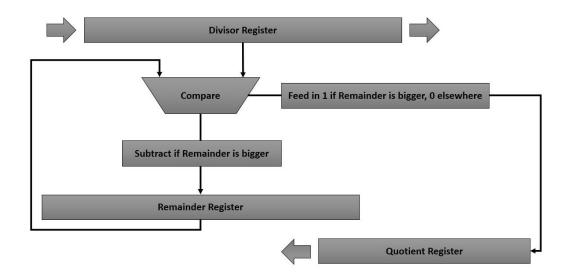

| 3.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DIVISION OPERATION CONSTRAINTS                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 3.3.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Normalize divisor constraint                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                  |

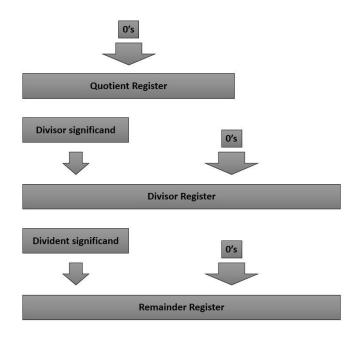

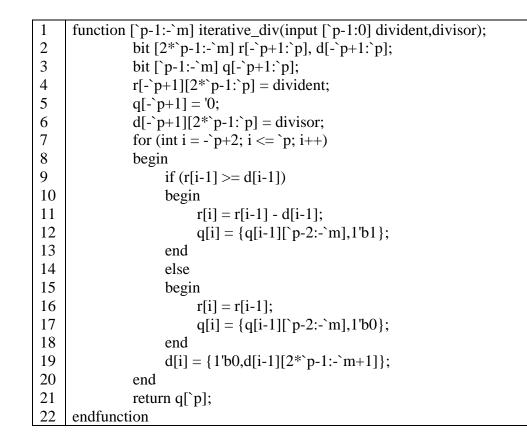

| 3.3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Division constraints                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                  |

| 3.3.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Carry/Leading zeroes correction                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                  |

| 3.3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Exception handling constraints                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                  |

| 3.4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FUSED MULTIPLY ADD CONSTRAINTS                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                  |

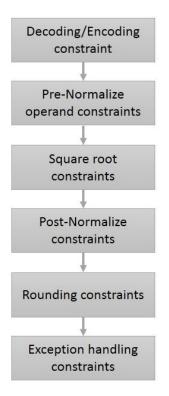

| 3.5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SQUARE ROOT CONSTRAINTS                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

| 3.5.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Decoding/Encoding constraints                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                  |

| 3.5.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Pre-Normalization step                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                  |

| 3.5.3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Square Root constraints                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | First Square root algorithm                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                  |

| 3.5.3.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Second Square root algorithm                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                                                                                                                               |