# DESIGN FOR YIELD FOR SUB-22nm FinFET-BASED FPGA

By

Mohamed Mohie El-Din Mohamed Aly Hassan

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

Electronics and Communications Engineering

# DESIGN FOR YIELD FOR SUB-22nm FinFET-BASED FPGA

By

# Mohamed Mohie El-Din Mohamed Aly Hassan

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

**Electronics and Communications Engineering**

Under the Supervision of

Prof. Dr. Hossam A. H. Fahmy

Dr. Hassan Mostafa

Professor

**Assistant Professor**

Electronics and Communication

Engineering Department

Faculty of Engineering, Cairo University

Electronics and Communication Engineering Department Faculty of Engineering, Cairo University

FACULTY OF ENGINEERING, CAIRO UNIVERSITY GIZA, EGYPT 2017

# DESIGN FOR YIELD FOR SUB-22nm FinFET-BASED FPGA

By

# Mohamed Mohie El-Din Mohamed Aly Hassan

A Thesis Submitted to the

Faculty of Engineering at Cairo University

in Partial Fulfillment of the

Requirements for the Degree of

MASTER OF SCIENCE

in

Electronics and Communications Engineering

Approved by the Examining Committee

Prof. Dr. Hossam A. H. Fahmy, Thesis Main Advisor

Prof. Dr. Mohamed Fathy, Internal Examiner

Prof. Dr. Mohamed Amin Ebrahim Dessouky, External Examiner (Electronics and Communications Engineering, Ain Shams University)

FACULTY OF ENGINEERING, CAIRO UNIVERSITY

GIZA, EGYPT

2017

**Engineer's Name:** Mohamed Mohie El-Din Mohamed

**Date of Birth:** 08/03/1990 **Nationality:** Egyptian

E-mail: Mohamed.mohie.hassan@gmail.com

**Phone:** +201068663016

**Address:** Electronics and Communications

Engineering Department,

Cairo University, Giza 12613, Egypt

**Registration Date:** 01/10/2011 **Awarding Date:** --/--/2017

**Degree:** Master of Science

**Department:** Electronics and Communications Engineering

**Supervisors:**

Prof. Dr. Hossam A. H. Fahmy

Dr. Hassan Mostafa

**Examiners:**

Prof. Dr. Hossam A. H. Fahmy (Thesis main advisor)

Prof. Dr. Mohamed Fathy (Internal examiner)

Prof. Dr. Mohamed Dessouky (External examiner)

(Electronics and Communication Engineering, Ain

Shams University)

## **Title of Thesis:**

Design For Yield For Sub-22nm FinFET-Based FPGA

# **Key Words:**

Design for Yield; Process Variations; FPGA; Leakage Power

# **Summary:**

In this thesis, a performance evaluation study for a FinFET-Based FPGA cluster under threshold voltage variation, representing the Die-to-Die variations, is launched with technology scaling starting from 20nm down to 7nm nodes showing the scaling trends of various performance metrics including the average power, delay, and power-delay product. Also some design insights and recommendations are proposed for the designers to achieve yield percentage of 99.87%. The leakage power is also studied for 14nm technology node under threshold voltage and temperature variations. Some solutions are implemented for leakage power control under threshold voltage variations including transistor stacking, minimum leakage vector, and gate sizing.

# Acknowledgments

I would like to express my utmost gratitude to Allah for giving me the strength to complete the work.

I would also like to sincerely thank my supervisors, Prof. Dr. Hossam Fahmy and Dr. Hassan Mostafa, for their continuous support and guidance throughout my work.

# **Table of Contents**

| ACKN   | OWLE           | DGMENTS                                                                   | I    |

|--------|----------------|---------------------------------------------------------------------------|------|

| TABLI  | E OF C         | ONTENTS                                                                   | II   |

| LIST ( | OF TAB         | BLES                                                                      | IV   |

| LIST ( | OF FIG         | URES                                                                      | V    |

| NOME   | ENCLA          | TURE                                                                      | VII  |

| ABSTI  | RACT           |                                                                           | VIII |

| CHAP'  | TER 1:         | : INTRODUCTION                                                            | 1    |

| 1.1.   | Mo             | TIVATION                                                                  | 1    |

| 1.2.   |                | GANIZATION OF THE THESIS                                                  |      |

| CHAP'  | TER 2 :        | : LITERATURE REVIEW                                                       | 3    |

| 2.1.   | Vai            | RIABILITY                                                                 | 3    |

| 2.1    | .1.            | Classification of variations                                              | 3    |

| 2      | 2.1.1.1.       | Die-to-Die (D2D) Variations                                               | 3    |

| 2      | 2.1.1.2.       | Within-Die (WID) Variations                                               | 3    |

| 2.1    | .2.            | Sources of variability                                                    | 4    |

|        | 2.1.2.1.       | Process Variations (Static Variations)                                    |      |

|        | 2.1.2.2.       | Environmental Variations (Dynamic Variations)                             |      |

| 2.1    | .3.            | Impact of Variability on the Frequency and Power                          | 9    |

| 2.1    | .4.            | State-of-Art Variations Mitigation Techniques                             | 11   |

| 2      | 2.1.4.1.       | CAD Tool and Statistical Design.                                          |      |

| _      | 2.1.4.2.       | Variations Mitigation at the Architecture Level                           |      |

| CHAP   | <b>TER 3</b> : | : FPGA UNDER STUDY                                                        | 14   |

| 3.1.   | FPC            | GAs                                                                       | 14   |

| 3.1    | .1.            | FPGA Logic Resources Architecture                                         | 16   |

| 3.1    | .2.            | FPGA Under Study                                                          | 16   |

| 3      | 3.1.2.1.       | Inverter                                                                  | 18   |

| 3      | 3.1.2.2.       | 2-By-1 Multiplexer                                                        | 20   |

|        | 3.1.2.3.       | Transmission Gate Flip Flop (TG-FF)                                       |      |

|        | 3.1.2.4.       | SRAM                                                                      |      |

|        | 3.1.2.5.       | FPGA 4-bit Lookup Table (LUT)                                             |      |

|        | 3.1.2.6.       | FPGA Cluster                                                              |      |

|        |                | : PERFORMANCE EVALUATION OF FINFET-BASI<br>NDER V <sub>TH</sub> VARIATION |      |

| 4.1.   |                | RODUCTION                                                                 |      |

| 4.1.   |                | FinFET Classification                                                     |      |

| 4.1    |                | Process Variations for FinFET                                             |      |

|        |                |                                                                           |      |

| 4.2.   |                | ULATION METHODOLOGY                                                       |      |

| 4.3.   |                | SULTS AND DISCUSSIONS                                                     |      |

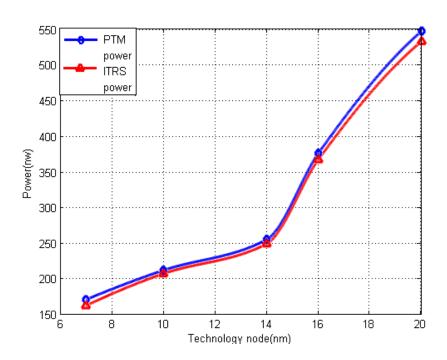

| 43     | : 1            | Average Power                                                             | 39   |

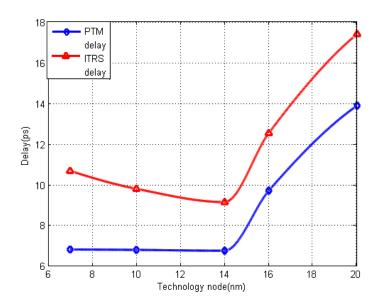

| 4.3.2.   | Delay                                                        | 42      |

|----------|--------------------------------------------------------------|---------|

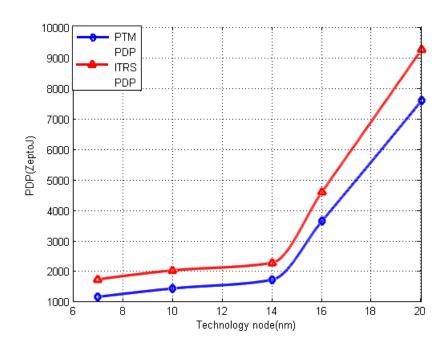

| 4.3.3.   | Power-Delay Product                                          | 42      |

| 4.4.     | DESIGN INSIGHTS                                              | 43      |

| 4.5.     | Conclusion.                                                  |         |

| CHADTEI  | R 5 : LEAKAGE POWER EVALUATION OF FINFET-BAS                 | ED EDCA |

|          |                                                              |         |

| CLUSTER  | R UNDER V <sub>TH</sub> VARIATION                            | 46      |

| 5.1.     | Introduction                                                 | 46      |

| 5.1.1.   | Leakage Current Sources                                      | 46      |

| 5.1.1.   | <u> </u>                                                     |         |

| 5.1.1.   | 2. Gate Leakage                                              | 48      |

| 5.1.2.   | Standby Leakage Reduction Techniques                         | 48      |

| 5.1.2.   |                                                              |         |

| 5.1.2.   | 2. Dual-Threshold Voltage                                    | 49      |

| 5.1.2.   | 3. Reverse Body Biasing                                      | 50      |

| 5.2.     | SIMULATION METHODOLOGY                                       | 51      |

| 5.3.     | RESULTS AND DISCUSSIONS                                      | 53      |

| 5.3.1.   | Leakage Power Segmentation and Loading Effect                | 53      |

| 5.3.2.   | Leakage Power Variation with V <sub>th</sub> and Temperature |         |

| 5.4.     | PROPOSED LEAKAGE POWER CONTROL TECHNIQUES                    |         |

| 5.4.1.   | Transistor Stacking                                          |         |

| 5.4.2.   | Minimum Leakage Vector (MLV)                                 |         |

| 5.4.3.   | Gate Sizing                                                  |         |

| 5.5.     | Conclusion                                                   |         |

| DISCUSSI | ON AND CONCLUSIONS                                           | 63      |

| REFEREN  | NCES                                                         | 64      |

|          |                                                              |         |

| ALLENDI  | X A: PTM MODELS                                              | 73      |

# **List of Tables**

| Table 3.1: Architecture decisions for the FPGA                             | 18 |

|----------------------------------------------------------------------------|----|

| Table 3.2: Inverter simulation measurements                                | 19 |

| Table 3.3: 2-to-1 simulation measurements                                  | 20 |

| Table 3.4: TG-FF simulation measurements                                   | 22 |

| Table 3.5: SRAM simulation measurements                                    | 23 |

| Table 3.6: Lookup Table simulation measurements                            | 25 |

| Table 3.7: Cluster 2-bit adder simulation measurements                     | 27 |

| Table 4.1: Simulated Device Parameters                                     | 38 |

| Table 4.2: Threshold Voltage Variations                                    | 39 |

| Table 5.1: Simulated Device Parameters                                     | 51 |

| Table 5.2: Threshold Voltage Variations                                    | 52 |

| Table 5.3: Leakage Power Values upon Stacking NFET and PFET                | 56 |

| Table 5.4: Tfin Optimized Values for Inverter                              | 60 |

| Table 5.5: Tfin Optimized Values for 2-to-1 Multiplexer                    | 60 |

| Table 5.6: Tfin Optimized Values for 6T SRAM                               | 61 |

| Table 5.7: Maximum Improvements and Delay Overhead for the Three Solutions |    |

| Table A.1: Key Technology Parameters                                       | 73 |

| Table A.2: PTM-MG Verification                                             | 74 |

# **List of Figures**

| Figure 2.1: Atomistic process simulation incorporating RDF and LER as the source intrinsic fluctuations. The green dots indicate the dopant atoms which determine the device's threshold voltage, while the blue dots indicate the drain/source doping [1]. Figure 2.2: Number of dopant atoms in the depletion layer of a MOSFET versus channel length Leff [7] | e<br>5<br>vith<br>7<br>e<br>8<br>or.<br>9<br>ing,<br>10 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Figure 2.9: The WID maximum critical path delay distribution for different values of                                                                                                                                                                                                                                                                             | of                                                      |

| independent critical paths Ncp. As Ncp increases, the mean of maximum critical pa                                                                                                                                                                                                                                                                                | th                                                      |

| delay increases [40]                                                                                                                                                                                                                                                                                                                                             |                                                         |

| Figure 3.1: Basic FPGA structure                                                                                                                                                                                                                                                                                                                                 | 15                                                      |

| Figure 3.2: Modern FPGA fabric                                                                                                                                                                                                                                                                                                                                   |                                                         |

| Figure 3.3: SRAM Programmer for logic and routing resources                                                                                                                                                                                                                                                                                                      |                                                         |

| Figure 3.4: A closer look at the tile of Island-Style FPGA                                                                                                                                                                                                                                                                                                       |                                                         |

| Figure 3.5: Structure of (a) Basic Logic Element (BLE) and (b) Logic cluster                                                                                                                                                                                                                                                                                     |                                                         |

| Figure 3.6: Sneak-path design in FPGA cluster                                                                                                                                                                                                                                                                                                                    |                                                         |

| Figure 3.7: Inverter schematic                                                                                                                                                                                                                                                                                                                                   |                                                         |

| Figure 3.8: Inverter simulation results.                                                                                                                                                                                                                                                                                                                         |                                                         |

| Figure 3.9: 2-to-1 MUX schematic                                                                                                                                                                                                                                                                                                                                 |                                                         |

| Figure 3.10: 2-to-1 MUX simulation results                                                                                                                                                                                                                                                                                                                       |                                                         |

| Figure 3.11: Transmission Gate Flip-Flop schematic                                                                                                                                                                                                                                                                                                               |                                                         |

| Figure 3.12: TG-FF simulation results                                                                                                                                                                                                                                                                                                                            |                                                         |

| Figure 3.13: SRAM structure and sizing                                                                                                                                                                                                                                                                                                                           |                                                         |

| Figure 3.14: SRAM simulation results (read operation)                                                                                                                                                                                                                                                                                                            |                                                         |

| Figure 3.15: SRAM simulation results (write operation)                                                                                                                                                                                                                                                                                                           |                                                         |

| Figure 3.16: Lookup table with 4 inputs and 16 SRAM cells                                                                                                                                                                                                                                                                                                        |                                                         |

| Figure 3.17: Lookup table simulation results                                                                                                                                                                                                                                                                                                                     |                                                         |

| Figure 3.18: FinFET-based FPGA cluster with 3 BLEs and 12 16-to-1 multiplexers                                                                                                                                                                                                                                                                                   |                                                         |

| Figure 3.19: CLB inputs                                                                                                                                                                                                                                                                                                                                          |                                                         |

| Figure 3.20: CLB outputs                                                                                                                                                                                                                                                                                                                                         |                                                         |

| Figure 4.1: Structural comparison between (a) planar MOSFET and (b) FinFET                                                                                                                                                                                                                                                                                       | 29                                                      |

| Figure 4.2: DIBL and sub-threshold swing (S) versus effective channel length for double-gate (DG) and bulk-silicon nFETs. The DG device is designed with an undo                                                                                                                                                                                                 | nod                                                     |

| body and a near-mid-gap gate material [59]                                                                                                                                                                                                                                                                                                                       | _                                                       |

| Figure 4.3: Structural comparison between (a) bulk and (b) SOI FinFETs                                                                                                                                                                                                                                                                                           |                                                         |

| Figure 4.4: Structural comparison between (a) FinFET and (b) Trigate FET                                                                                                                                                                                                                                                                                         |                                                         |

| Figure 4.5: Structural comparison between (a) SG and (b) IG FinFET                                                                                                                                                                                                                                                                                               |                                                         |

| Figure 4.6: Drain current (IDS) versus front-gate voltage (VGFS) for three nFinFETs                    |     |

|--------------------------------------------------------------------------------------------------------|-----|

|                                                                                                        | 35  |

| Figure 4.7: Drain current (IDS) versus front-gate voltage (VGFS) for three pFinFETs                    |     |

| L J                                                                                                    | .35 |

| Figure 4.8: Distribution of leakage current (I <sub>OFF</sub> ) for different process parameters, each |     |

|                                                                                                        | 36  |

| Figure 4.9: I <sub>OFF</sub> versus temperature for three nFinFETs [80]                                | 37  |

| Figure 4.10: Distribution of IOFF under process variations for three nFinFETs [80]                     | 38  |

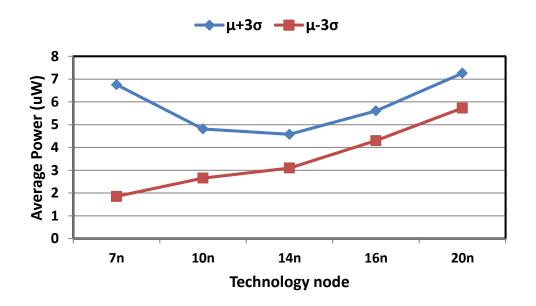

| Figure 4.11: Average power variation percentages with Vth variation for various                        |     |

| technology nodes [90]                                                                                  | 40  |

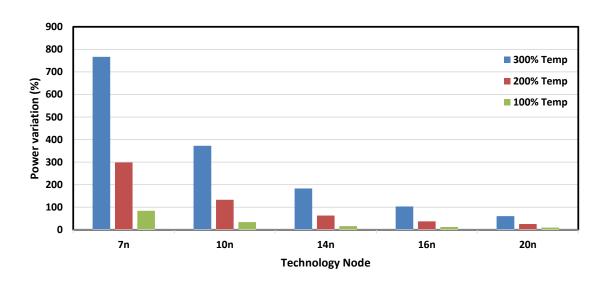

| Figure 4.12: Average power variation percentages with temperature variation for                        |     |

| various technology nodes                                                                               | 40  |

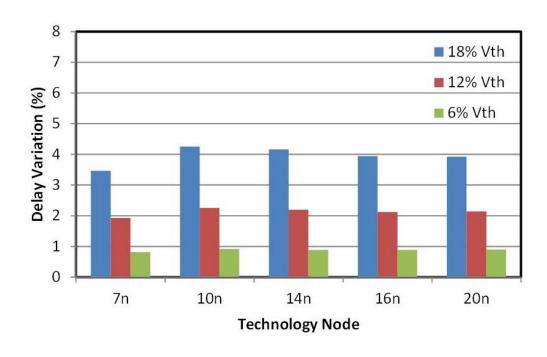

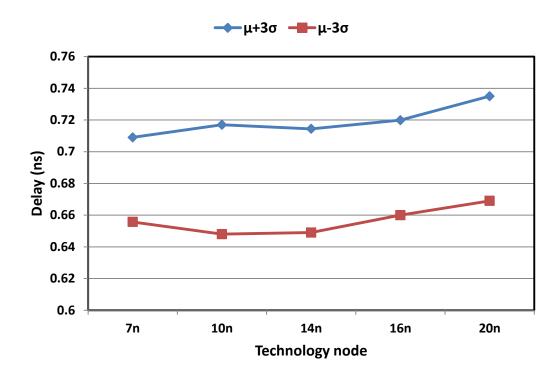

| Figure 4.13: Delay variation percentages with Vth variation for various technology                     |     |

|                                                                                                        | 41  |

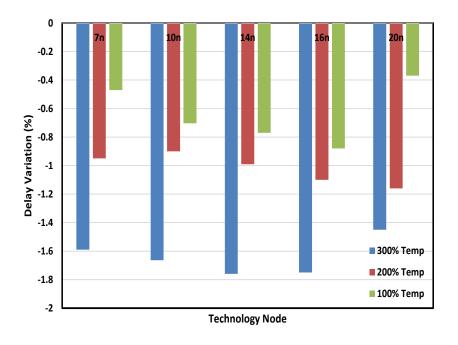

| Figure 4.14: Delay variation percentages with temperature variation for various                        |     |

|                                                                                                        | 41  |

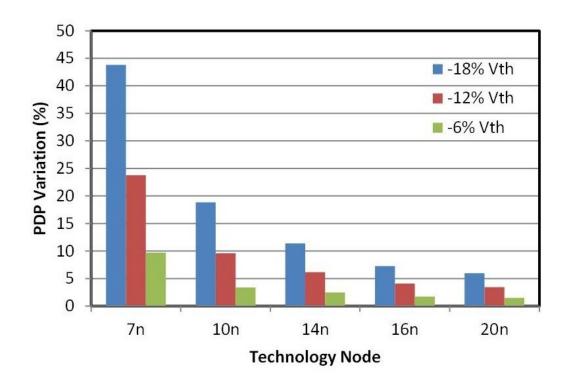

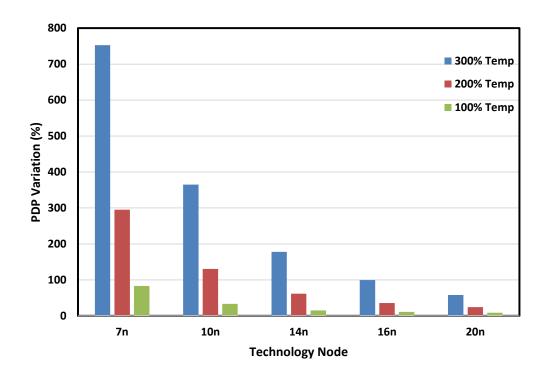

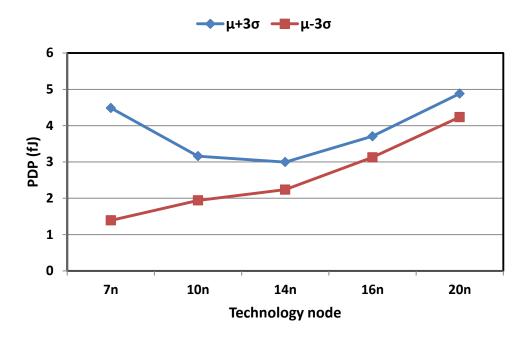

| Figure 4.15: PDP variation percentages with Vth variation for various technology noc                   | des |

|                                                                                                        | 42  |

| Figure 4.16: PDP variation percentages with temperature variation for various                          |     |

| technology nodes                                                                                       | 43  |

| Figure 4.17: Power constraints with Vth for various technology nodes [90]                              | 44  |

| Figure 4.18: Delay constraints with Vth for various technology nodes [90]                              |     |

| Figure 4.19: PDP constraints with Vth for various technology nodes [90]                                |     |

| Figure 5.1: Leakage current sources in deep submicron devices [47]                                     |     |

| Figure 5.2: Gate leakage dominant states in FPGA pass-transistor device                                |     |

| Figure 5.3: Multi-Threshold CMOS (MTCMOS)                                                              |     |

| Figure 5.4: Dual-threshold voltage technique                                                           |     |

| Figure 5.5: Reverse Body Biasing (RBB)                                                                 |     |

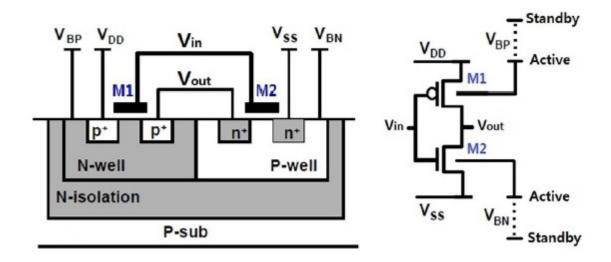

| Figure 5.6: Vth variations sources in FinFET devices, σVth [mV]                                        |     |

|                                                                                                        |     |

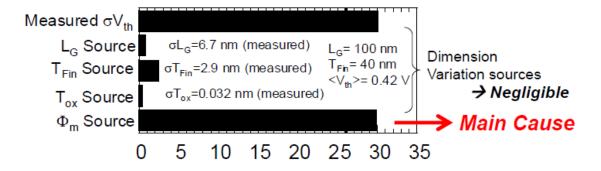

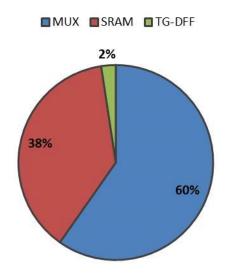

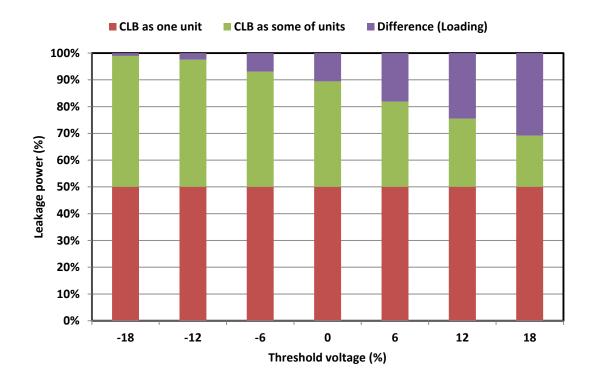

| Figure 5.8: Leakage power segmentation                                                                 | -   |

| of the units comprising the cluster with the difference representing the loading effect.               |     |

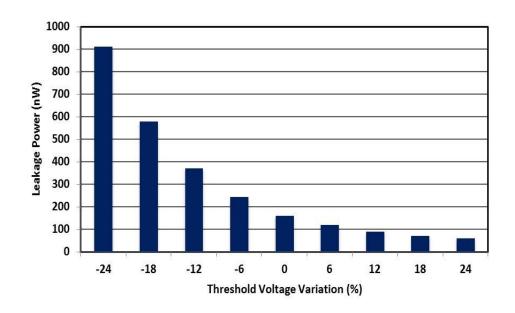

| Figure 5.9: Leakage power variation with Vth variation                                                 |     |

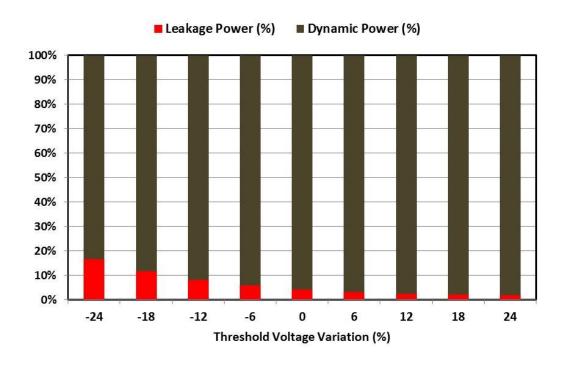

| Figure 5.10: Dynamic and leakage power consumption percentages with Vth variation                      |     |

|                                                                                                        |     |

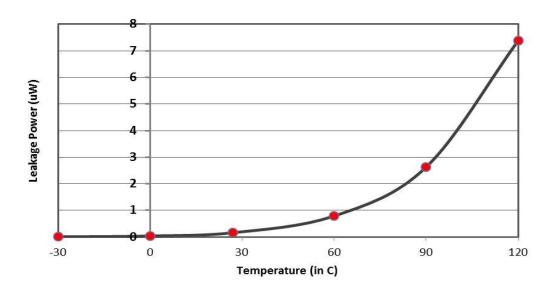

| Figure 5.11: Temperature dependency of leakage power                                                   |     |

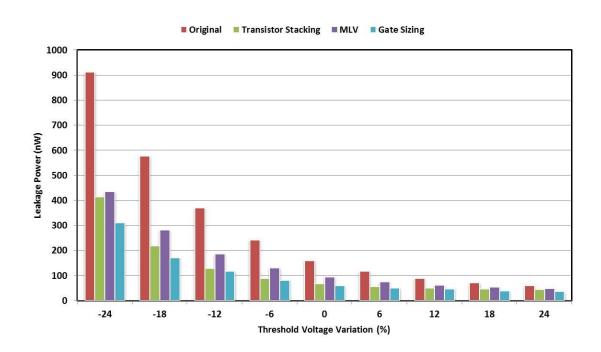

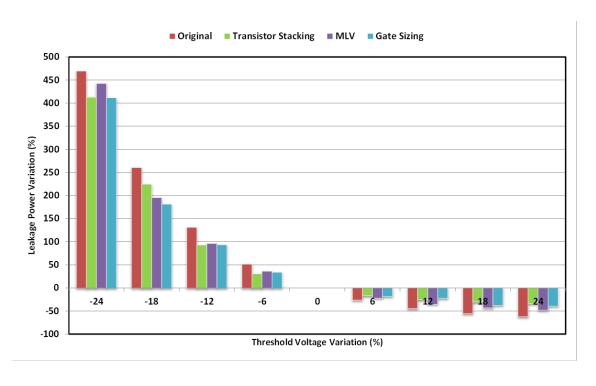

| Figure 5.12: Leakage power with Vth variation for the three solutions                                  |     |

| Figure 5.12: Leakage power with vin variation for the three solutions                                  |     |

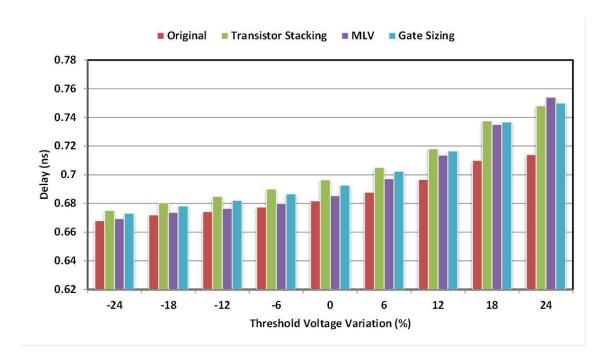

| Figure 5.14: Delay overhead with Vth variation for the three solutions                                 |     |

|                                                                                                        |     |

| Figure 5.15: FinFET Inverter                                                                           |     |

| Figure 5.16: FinFET 2-to-1 multiplexer                                                                 |     |

| Figure 5.17: FinFET 6T SRAM cell                                                                       |     |

| Figure A.1: The difference between ITRS off-current and PTM off-current impact on                      |     |

| TG-FF power [123]                                                                                      |     |

| Figure A.2: The difference between ITRS off-current and PTM off-current impact on                      |     |

| TG-FF delay [123]                                                                                      |     |

| Figure A.3: The difference between ITRS off-current and PTM off-current impact on                      |     |

| TG-FF PDP [123]                                                                                        | 15  |

# **Nomenclature**

ADE Analog Design Environment

ASIC Application-Specific Integrated Circuits

BLE Basic Logic Element

BSIM Berkley Short-channel IGFET Model

CAD Computer-Aided Design

CMG Common Multi-Gate

CMOS Complementary Metal-Oxide Semiconductor

DIBL Drain-Induced Barrier Lowering

DLL Delay-Locked Loop

D2D Die-to-Die

FinFET Fin Field Effect Transistor

FPGA Field-Programmable Gate Array

GIDL Gate-Induced Drain Leakage

IGFET Independent-Gate FET

LER Line-Edge Roughness

LSTP Low Standby Power Devices

LUT Look-Up Table

NWE Narrow Width Effects

OPE Optical Proximity Effects

PDF Probability Density Function

PDP Power-Delay Product

PLL Phase-Locked Loop

RDF Random Dopant Fluctuations

SCE Short Channel Effects

SGFET Shorted-Gate FET

SoPC System-on-a-Programmable-Chip

SRAM Static Random Access Memory

SSTA Statistical Static Timing Analysis

WID Within-Die

# **Abstract**

As CMOS technology is scaled towards the deep sub-micron regime, digital circuits' designers are facing increased variability in form of either process variations or environmental variations. Those variations are classified to Die-to-Die variations and Within-Die variations. Our work presented in this thesis aims at evaluating the performance of a FinFET-Based FPGA cluster under threshold voltage variation that represents the Die-to-Die variations with technology scaling starting from 20nm down to 7nm nodes using Berkley Predictive Technology Models, showing the scaling trends of different performance metrics including the average power, delay, and power-delay product. Some design insights and recommendations are proposed for the designers to achieve yield percentage of 99.87%.

Since the leakage power is much more pronounced in advanced technology nodes, we also studied the leakage power and its variation for 14nm technology node under threshold voltage and temperature variations. The results emphasized the log-normal dependency of the leakage power on the threshold voltage and also the exponential dependency with temperature. Some solutions are proposed and implemented for leakage power control under threshold voltage variation including transistor stacking, minimum leakage vector (MLV), and gate sizing. These solutions have shown improvements for both the leakage power and leakage power variation, but also these solutions introduced a minor delay and area overheads which are reported and compared as well.

The FPGA cluster we built for our study is configured to a 2-bit adder benchmark used for both the performance evaluation study with technology scaling and the leakage power evaluation study as well. Cadence Virtuoso and ADE-GXL are used for both FPGA cluster building and simulations respectively.

# **Chapter 1: Introduction**

This chapter presents a short introduction about the significance of studying the effect of process variations while scaling down CMOS technologies coming to different FinFET technologies. Section 1.1 presents the motive behind this research work. Section 1.2 provides the thesis outline and organization.

# 1.1. Motivation

More than four decades of scaling CMOS technology has been the biggest driver for electronics industry. CMOS transistor scaling allowed building chips with billions of transistors in modern Integrated Circuits (ICs) and a broad range of electronic products with very high integration levels [1]. Nevertheless, the continued rigorous scaling of CMOS technology in sub-100nm regime has created massive design challenges, especially when transitioning to advanced technology nodes starting from 22nm technology. Assignable to process control limitations, manufacturing tolerances in process technology are not equally scaling as the transistor channel length [2-5]. Furthermore, process variations due to fundamental physical limits such as Line-End Roughness (LER) and Random Dopant Fluctuations (RDF) are significantly increasing with technology scaling [2, 6-11]. Consequently, statistical parameter variations are getting worse with consecutive technology generations, and variability is currently becoming one of the biggest challenges that face the semiconductor industry, resulting in huge yield losses [5]. That variability has been affecting analog design for some considerable time, and currently it is significantly impacting digital design at nanometer technology nodes. In addition, scaling the threshold voltage in nanometer regime posed a massive increase in the sub-threshold leakage current due to the exponential dependence, hence affecting the power efficiency which is becoming the key to sustaining continually enhanced performance for future VLSI circuits,

# 1.2. Organization of the Thesis

In order to have an overview about the process variations effects on the next generation FPGAs incorporating FinFETs devices in the manufacturing process, it is important to study the variations effects on the basic performance metrics such as the average power, delay, and power-delay product.

An introduction about the process variations in general, their sources and impacts on the digital circuits, is illustrated in Chapter 2. Chapter 3 gives an introduction about FPGAs, their structures, and the FPGA cluster we used for our study. It also contains the description of each unit comprising the FPGA cluster along with its simulation waveforms and measurements for basic performance metrics such as power, delay, and power-delay product (PDP).

In Chapter 4, we study the impact of threshold voltage variation with, representing D2D variations, with FinFET technology scaling from 20nm down to 7nm over the

FPGA cluster we built for our evaluation study. Also some design insights are presented in this chapter that help achieving a yield percentage of 99.87%.

Since the leakage power is becoming much more pronounced with the continued technology scaling, Chapter 5 presents the work done in order to study the leakage power variation with both the threshold voltage and temperature on the FPGA cluster. Also some solutions are proposed and implemented in order to control the leakage power for 14nm node.

And finally, the conclusion and the potential future work are drawn in "Discussion and Conclusions" section.

Appendix A illustrates the PTM models we used in our simulation in detail.

# **Chapter 2: Literature Review**

This chapter is organized as follows: Section 2.1 discusses the variability sources and classifications, the impact of variations on the frequency and power, and some variations mitigation techniques. Section 2.2 discusses the FPGA as the platform of our study, the FPGA architecture in terms of both the logic and routing resources, and also the structure and specifications of the FPGA cluster we used in this research work.

# 2.1. Variability

Variations in integrated circuits are basically the deviations from the intended or designed values for a structure or circuit parameter in concern. Usually, the variations are caused by two different sources: physical factors and environmental factors. The physical factors cause a permanent variation in device parameters and they are generally caused by the lack of exact controls and statistical variations during the fabrication process [12]. Regarding the environmental factors, they cause variations in the circuit operation while the circuit is functioning, and they include variations in the power supply and temperature.

## 2.1.1. Classification of variations

The variations sources can generally be categorized into two classes [4, 9, 12, 13]:

## 2.1.1.1. Die-to-Die (D2D) Variations

The D2D variations are also called inter-die or global variations. They are variations from die to die and, in the same way, they affect all devices on the same chip (for example, they may cause all the transistors' threshold voltages or gate lengths' on the same die to deviate from their nominal values by the same amount). These variations are generally independent and hence, they can be represented by a single value for each die. These variations are generally assumed to have a Gaussian distribution with a given variance [12], and they represent a shift in the parameter's mean from its nominal value. D2D variations in a single process parameter are dealt with using corner-based models which assume that all the devices on a given design sample have a value that is shifted from the mean by a fixed amount [12].

## 2.1.1.2. Within-Die (WID) Variations

The WID variations are also called intra-die or local variations. These variations cause transistor parameters to vary across different devices within the same die (for example, some devices may have larger channel length than the rest of the devices on the same die). Thus, each device on a die requires a separate random

variable that represents its WID variations. WID variations can be subdivided further into two classes: [13].

#### 1- Random Variations

They are spatially uncorrelated variations which result from statistical quantization effects, such as RDF and LER. The impact of these random variations is expected to be worse with process parameters scaling, and they can be characterized by their statistical distribution. The random variations' impact can be alleviated by means of increasing the logic depth because of the averaging effect. Unfortunately, the trend to boost the clock frequency of a design using aggressive pipelining has resulted in smaller logic depth which, hence, increases the impact of this type of variations.

# 2- Systematic Variations

These variations are usually caused by physical phenomena such as distortions in the lens and some elements in the lithographic system. This type of variations is quite complicated to be modeled; therefore, they are usually modeled as random variations with certain value of spatial correlation. All the variations that are layout-dependent, such as channel width and length variations, are considered systematic variations as well.

# 2.1.2. Sources of variability

## 2.1.2.1. Process Variations (Static Variations)

Process variations impact the device structure and, thus, they alter the circuits' electrical properties. The process variations' sources can be outlined as follows:

#### 1- Random Dopants Fluctuations (RDF)

With CMOS technology scaling, the number of doping impurities in the channel depletion layer decreases, especially with minimum geometry devices. The atomicity of the dopants in the channel does not allow a constant concentration of dopants to appear across the channel as shown in Figure 2.1. Thus, it is very unlikely to have two neighboring transistors with the same number and placement of dopants. This random number and placement of the dopants cause uncertainty in the transistor threshold voltage, Vth. The statistical distribution of Vth due to RDF is found to follow a normal distribution [14, 15]. The standard deviation of Vth distribution due to RDF is modeled as [16, 17]:

$$\sigma_{V_{th}} = \sqrt[4]{4q^3 \epsilon_{Si} N_a \varphi_F} \frac{T_{ox}}{\epsilon_{ox}} \frac{1}{\sqrt{3W*L}}$$

(2.1)

where q is the electron charge,  $\epsilon_{ox}$  and  $\epsilon_{Si}$  are the dielectric constants of the gate oxide and silicon respectively, Na is the channel dopant concentration,  $\varphi_F$  is the difference between intrinsic level and Fermi level,

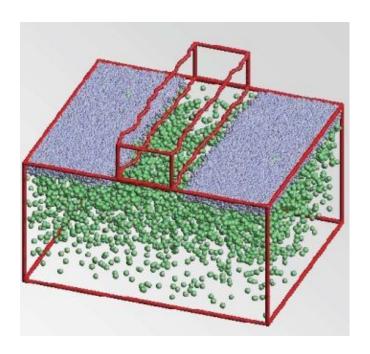

Figure 2.1: Atomistic process simulation incorporating RDF and LER as the sources of intrinsic fluctuations. The green dots indicate the dopant atoms which determine the device's threshold voltage, while the blue dots indicate the drain/source doping [1]

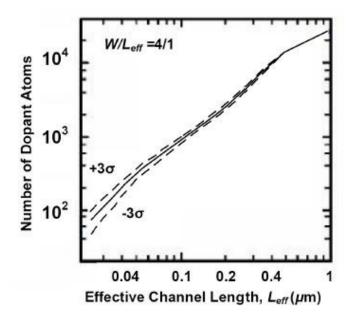

Figure 2.2: Number of dopant atoms in the depletion layer of a MOSFET versus channel length Leff [7]

$T_{ox}$  is the gate oxide thickness, and L and W are the channel length and width respectively. Equation (2.1) shows that  $\sigma_{V_{th}}$  is inversely proportional to the square root of the active device area. Thus, sizing up the transistors can help mitigating these variations, which is one of the most commonly used techniques in analog circuit design to decrease transistors mismatch [18]. Moreover, for SRAM cells which typically have minimum size devices,  $\sigma_{V_{th}}$  will be the largest. Figure 2.2 shows that with technology scaling, the RDF variations ( $\sigma_{V_{th}}$ ) experience a large increase which may reach up to 50% of  $V_{th}$  in advanced technology nodes, causing a large spread in performance and power.

# 2- Channel Length Variations

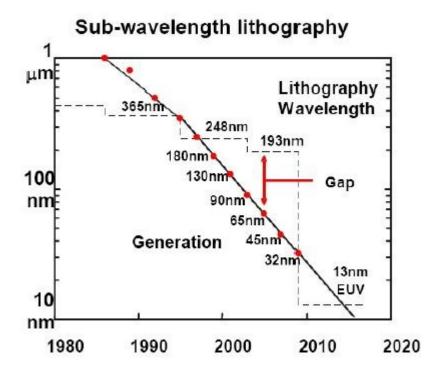

The patterning of design features with smaller dimensions than the light wavelength, used in optical lithography, results in distortions due to light diffraction, which is called Optical Proximity Effects (OPEs) [4, 12]. These effects are expected to worsen with technology scaling as the light wavelength is not scaling with the same pace as the device feature size, as shown in Figure 2.3. The OPEs will make it very challenging to print precise patterns on the Silicon wafer with technology scaling [19], making the lithography at these small feature sizes very challenging. OPEs are layout dependent, resulting in different Critical Dimension (CD) variations depending on neighboring lines and the orientation [13]. Controlling these variations has become very challenging in current technologies, and is expected to increase for future technology nodes [9].

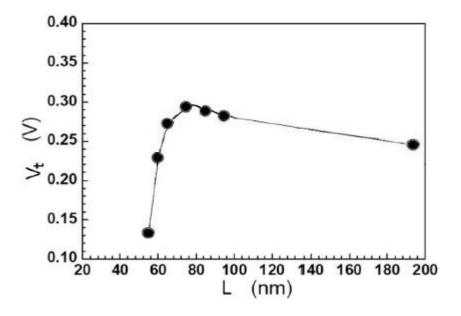

The variation in transistor's channel length has a direct effect on the transistor electrical parameters; however, the most impacted parameters are the transistor's threshold voltage  $V_{th}$  [15, 20, 21]. This is due to the exponential dependence of  $V_{th}$  on channel length L for short channel devices, specifically due to Drain Induced Barrier Lowering (DIBL) effect. DIBL causes  $V_{th}$  to be substantially dependent on L as shown in Figure 2.4. This dependence can be modeled as [15, 20, 21]:

$$V_{th} \approx V_{tho} - (\xi + \eta V_{DS}) \exp(\frac{L}{L_{to}})$$

(2.2)

where  $V_{tho}$  is the long channel threshold voltage,  $\xi$  is the charge sharing coefficient,  $L_{to}$  is the characteristic length, and  $\eta$  is the DIBL coefficient. Accordingly, a slight variation in L will introduce huge variation in  $V_{th}$  as shown in Figure 2.4.

# 3- Line-Edge Roughness (LER)

LER refers to the roughness introduced on the channel edge during the gate patterning, as shown in Figure 2.1, which contributes to the threshold voltage variations. Previously, the amount of this introduced LER was insignificant compared to the dimensions of the transistor channel (on the

Figure 2.3: Lithography wavelength scaling for different technology nodes [6]

Figure 2.4: Measured Vth versus channel length L for a 90nm CMOS technology with shows strong short channel effects causing sharp roll-off for Vth for shorter L [15]

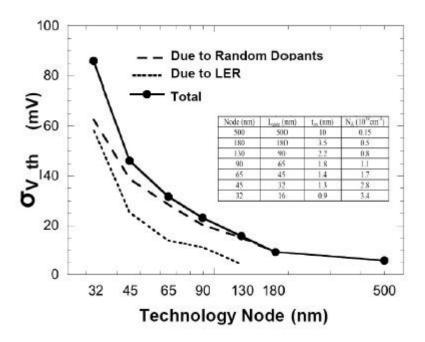

order of 5 nm) and also much smaller than the CD variations. However, with the continued transistor scaling, that introduced roughness becomes a significant source of variations in transistor's characteristics since it does not scale correspondingly [22]. These random effects cause variations in transistor's threshold voltage. Figure 2.5 shows the predicted variations in threshold voltage due to both LER and RDF versus technology nodes [1, 8] showing that for sub-32 technology nodes, threshold voltage variations due to LER and RDF will be comparable.

## 4- Gate Oxide Thickness Variations

Variations in the oxide thickness  $T_{ox}$  affect many electrical parameters of the device, especially the transistor threshold voltage  $V_{th}$ . Therefore, the  $T_{ox}$  variations should be considered.

#### 5- Channel Width Variations

Transistor channel width (W) will have variations as well due to the lithography limitations. These channel width variations will contribute to V<sub>th</sub> variations due to the Narrow-Width-Effects (NWEs), which cause V<sub>th</sub> to be dependent on W. However, the impact of W variation on V<sub>th</sub> can be considered very minimal compared to the impact due to L variations since W is typically 3-4 times larger than L [23].

Figure 2.5: Predicted  $\sigma_{V_{th}}$  including RDF and LER versus technology nodes for the smallest transistor. The inset shows the technological parameters used [8]

## 2.1.2.2. Environmental Variations (Dynamic Variations)

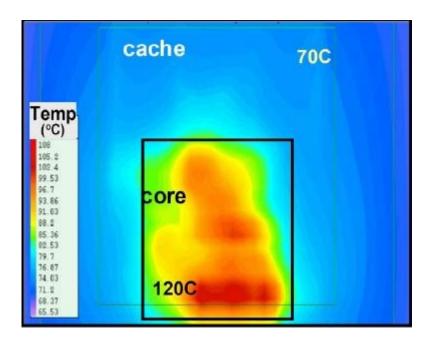

Environmental variations impact the circuit operation while the circuit is functioning. They include variations in both the supply voltage and the temperature of the chip or across the chip [6, 9]. Variations in power supply are mainly due to the switching activity variations within the die that are dependent on the input vectors. A reduced power supply lowers the drive strength of the transistors and, consequently, causes performance degradation [13]. This reduction in the power supply will be problematic with technology scaling since the headroom between the supply voltage and the device's threshold voltage is being reduced consistently [24]. WID temperature variations are considered one of the major performance and packaging challenges as both device and interconnect exhibit temperature dependence that results in performance degradation at higher temperature. Moreover, temperature variations across different blocks communicating on the same die may result in performance mismatch, which may lead to functional failures [4]. Figure 2.6 shows WID temperature fluctuations for a microprocessor unit, with the core exhibiting a hot spot of 120°C [25].

Figure 2.6: Thermal profile showing WID temperature variation for a microprocessor. Hot spots with temperatures as high as 120°C are shown [25]

# 2.1.3. Impact of Variability on the Frequency and Power

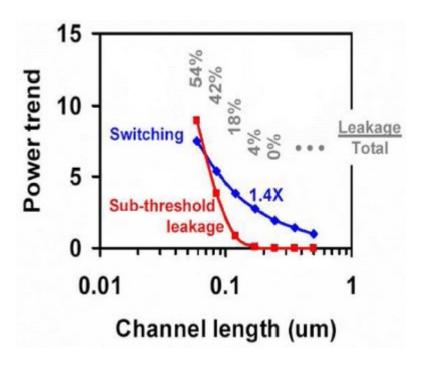

In the nanometer regime, the reduction of the threshold voltage causes a substantial increase in the device sub-threshold leakage current which flows between the drain and source of a transistor when  $V_{GS}$  is less than the transistor's threshold voltage  $V_{th}$  [7, 26]. Sub-threshold leakage current has an exponential dependence on the threshold voltage. Furthermore, sub-threshold leakage is also very sensitive to temperature, doubling for every  $8^{\circ}K$  to  $10^{\circ}K$  temperature increase [27]. Leakage power is considered a very

significant portion of the total power consumed in sub-90nm technology nodes. It is expected that the leakage power can reach up to more than 50% at 45nm technology, as shown in Figure 2.7.

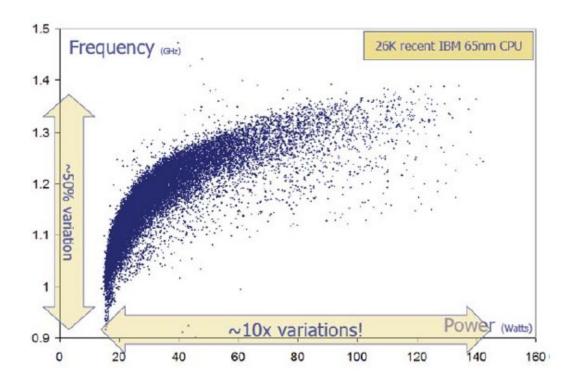

The large variability in advanced CMOS technology nodes plays an important role in determining the total chip leakage [28]. This has underlined the need to take statistical leakage variations into consideration during the design cycle [28, 29]. Figure 2.8 shows the measured variations for both leakage power and frequency for 65nm technology node which illustrates that there is a leakage variation about 10X for a 50% variation in chip frequency [30].

According to [25], a large percentage of the chips that meet the required operating frequency constraint dissipate a huge amount of leakage power. This makes them inconvenient for usage and, accordingly, causes yield degradation. This is due to the trade-off between leakage current and circuit performance. For devices with smaller  $V_{th}$  than nominal due to channel length variations, the sub-threshold leakage current increases exponentially. Meanwhile, the circuit delay decreases with increasing the driving current,  $I_D$ , since the overdrive voltage  $(V_{DD}-V_{th})$  is increased. Thus, those chips have higher operating frequency, but they suffer from huge leakage which makes them unacceptable [6, 25, 31].

Figure 2.7: Dynamic (switching) and static (leakage) power versus technology scaling, showing the exponential increase in leakage power [26]

Figure 2.8: Leakage and frequency variations for IBM processor in 65nm technology [30]

# 2.1.4. State-of-Art Variations Mitigation Techniques

In this subsection, we discuss couple of state-of-art related research dealing with the increase in variability in nanometer regime in order to improve the yield. The first method is using Computer Aided Design (CAD) tools and statistical design which attempt to model the variations in the design flow cycle. And the second method attempts to deal with variations at the architecture level.

## 2.1.4.1. CAD Tool and Statistical Design

Recently, a large number of research work has been made in the area of CAD tools that attempt to account and model the random variations at the design flow level. One of the most researched topics in this area is Statistical Static Timing Analysis (SSTA) [9, 13, 21, 32, and 33]. In SSTA, the circuit delay is

Basically considered a random variable and SSTA then calculates the probability density function (PDF) of the delay at a certain defined path [9]. Similar to the SSTA which is used to model the delay variations, few research work targets modeling the process variations effects on other metrics including leakage power, noise margins, and soft errors [34-38].

Statistical design aims at statistically altering the circuit parameters at the design phase in order to reduce the process variations' impact and increase both the circuit robustness and the yield. One of the most common statistical design techniques is statistical gate sizing at which either the length or width of the transistor is tweaked to modulate the current drive capability. For

example, process variations may increase the circuit delay, the statistical gate sizing algorithms are proposed to reduce the mean and standard deviation of the delay variations and, thus, improve the timing yield [32, 33].

# 2.1.4.2. Variations Mitigation at the Architecture Level

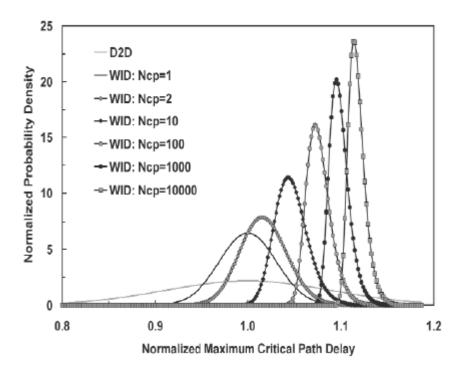

One of the first pieces of work that related variability to architecture was the work introduced by Bowman et a.l [39-41], and presented a statistical predictive model for the maximum operating frequency (FMAX) distribution in the presence of process variations in a chip. This technique provides insights on the impact of different components of variations on the FMAX distribution. The WID delay distribution heavily depends on the total number of independent critical paths for the entire chip N<sub>cp</sub>. For a larger number of critical paths, the mean value of the maximum critical path delay increases, as shown in Figure 2.9. As the number of critical paths increases, the probability that anyone of them will be strongly impacted by process variations becomes higher, and as a result, increases the mean of critical path delay. On the other hand, the delay's standard deviation (or delay spread) decreases with larger N<sub>cp</sub>, thus making the spread of the overall critical path determined mainly by D2D variations. The results showed that WID variations directly affect the mean of the maximum frequency, while D2D fluctuations affect the variance.

Figure 2.9: The WID maximum critical path delay distribution for different values of independent critical paths Ncp. As Ncp increases, the mean of maximum critical path delay increases [40]

Another factor that impacts the delay distribution is the logic depth per critical path. The impact of logic depth on delay distribution is different when dealing with random or systematic WID variations. Random WID variations have an averaging effect on the overall critical path distribution, while systematic WID variations affect all the gates on the path, hence, increase delay spread.

Other variation-tolerant research work at the architectural level was presented in [42], where a statistical methodology for pipeline delay analysis was presented. The importance of logic depth in variability research studies was accentuated, and it was shown that the change in logic depth and imbalance between stage delays can greatly improve the yield of a pipeline. Techniques such as deep pipelining and the push for high clock speeds decreases logic depth and have an undesirable impact on design variability [42].

# **Chapter 3 : FPGA Under Study**

This chapter gives an introduction about the Field-Programmable Gate Arrays (FPGAs) and presents a detailed explanation for each unit used to build the FPGA cluster and also simulation waveforms for each unit comprising the cluster. Also measurements for basic metrics (average power, delay, and power-delay product) are tabulated for each unit.

# 3.1. **FPGAs**

In order to sustain reprogrammable and easily reconfigurable designs with flexible prototyping capabilities and enhanced performance, taking advantage of hardware parallelism, Field-Programmable Gate Arrays (FPGAs) are being used in production as reliable candidates in electronic design in terms of performance, time to market, and long-term maintenance. In addition, FPGA-based hardware solutions are considered the most cost-aware solutions when it comes to decreasing the nonrecurring engineering (NRE) expenses. This is mainly due to the continuous change in system requirements and design specifications over time, compared to custom Application-Specific Integrated Circuits (ASIC) designs which endure far more NRE expenses.

There are two main platforms dominating the programmable logic devices market; FPGAs and Complex PLDs (CPLDs). FPGAs mostly incorporate Look-up Tables (LUTs) to implement the logic functions, while CPLDs use the sum-of-products approach for implementing the logic functions. Lately, FPGA vendors offered a comprehensive, alternative platform to FPGA for large volume production demands called structured ASICs [43, 44].

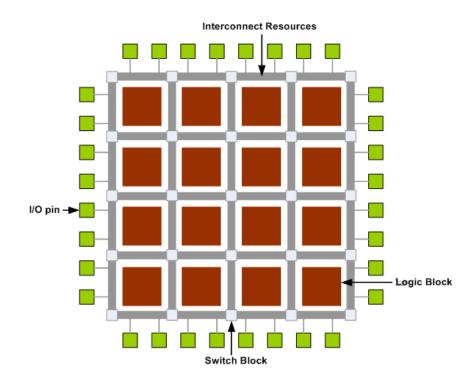

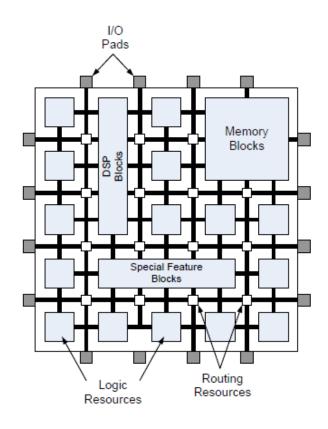

Traditionally, FPGAs basic structure, as shown in Figure 3.1, consist of input/output pads, array programmable logic resources embedded in a sea of programmable interconnects that are configurable to implement any logic function with the possibility of augmenting memory and multiplier blocks. However, state-of-the-art FPGAs usually include Digital Signal Processing (DSP) blocks, embedded memory, Phase-Locked Loops (PLLs), and other special feature blocks as shown in Figure 3.2. These features made FPGAs to be an appealing alternative for some System-on-a-Programmable-Chip (SoPC) designs.

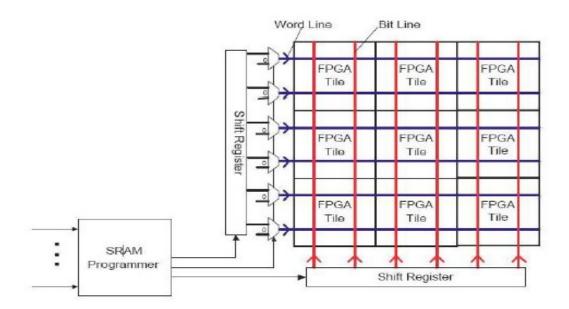

The technology used in programming both logic and the interconnect resources within the FPGAs can be flash memory [45], antifuse [46,47], or Static Random Access Memory (SRAM). For the SRAM-based FPGAs, they offer in-circuit re-configurability at the expense of volatility, while antifuse-based FPGAs are write-once devices. Flash-based FPGAs provide an intermediate solution by providing re-configurability as well as non-volatility. The most widely used programming technology in FPGAs now is SRAM as shown in Figure 3.3.

Figure 3.1: Basic FPGA structure

Figure 3.2: Modern FPGA fabric

Figure 3.3: SRAM Programmer for logic and routing resources

# 3.1.1. FPGA Logic Resources Architecture

The logic blocks within FPGAs are mainly responsible for implementing the functionality needed by each application. Increasing the logic blocks' size, i.e., increasing the number of inputs to each logic block, increases the number of logic functions that could be performed by each logic block and also improves the delay/area performance of the logic block [48, 49]. However, this comes on the expense of wasted resources since logic blocks will not have all of their inputs fully utilized.

Currently, most commercial FPGAs incorporate LUTs to implement the logic blocks. A k-input LUT basically consists of  $2^k$  configuration bits by which the required truth table is programmed during the configuration stage. The almost standard number of inputs for LUTs is four, which was proven optimum for both area and delay objectives [49]. However, this number can vary depending on the targeted application.

# 3.1.2. FPGA Under Study

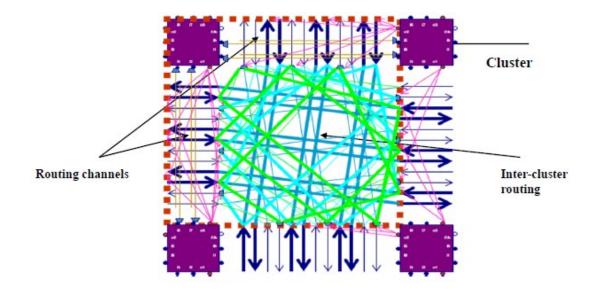

The targeted FPGA built used in our study is an Island-style FPGA which consists of 2-dimensional array of repeated tiles, each consists of a logic cluster block, routing channels to connect inputs and outputs to the clusters, and Inter-cluster routing in order to connect clusters with each other. One level down of hierarchy of the tile is shown in Figure 3.4. Some previous work was done to study different configurations of FinFET-based FPGA LUTs [50] implemented using 16nm technology and simulated using HSPICE. The metrics used to evaluate the different candidate LUTs were the delay, energy, and the layout area.

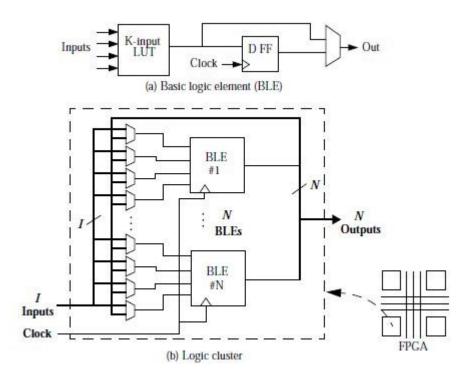

In this research work, we have built FinFET-based FPGA logic cluster on schematic level using Cadence Virtuoso as shown in Figure 3.5. It consists of three basic logic elements (BLE), each BLE encapsulates a LUT with size of 4 (four inputs), D-Flip-Flop, and 2-to-1 multiplexer to select either the registered or unregistered LUT output. Both the cluster size, N and the LUT size, K have been obtained by experimentally

Figure 3.4: A closer look at the tile of Island-Style FPGA

Figure 3.5: Structure of (a) Basic Logic Element (BLE) and (b) Logic cluster

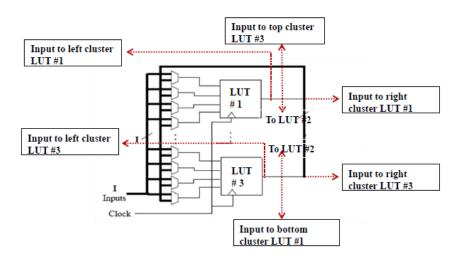

deriving the relationship between the number of cluster logic inputs required to achieve utilization percentage of 98% as a function of K and N [49]. This is  $=\frac{K}{2} \times (N+1)$ , where I is the number of distinct cluster inputs (8 in our case, as reported in Table 3.1). Generally, we have in our design 11 inputs to the logic cluster, eight of them are distinct inputs while the other three LUTs which makes the output of each LUT available for direct connection to one of the inputs of the nearby LUTs in the same cluster which implies the "fully connected" approach; This means that all I cluster inputs and N outputs can be connected to each of the K inputs on every LUT. This, as a result, increases the FPGA speed by saving the number of inputs and bypassing the long capacitive routing channels as shown in Figure 3.6.

The following subsections will discuss the units comprising the cluster with the accompanied simulations and measurements. The models used in this research work for simulations are PTM-CMG models, described in Appendix A. The sizing of the transistors is only one fin per transistor unless otherwise stated in the circuit schematic.

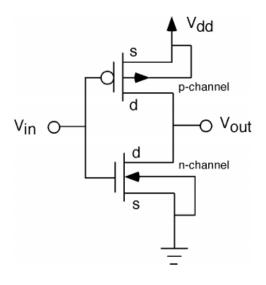

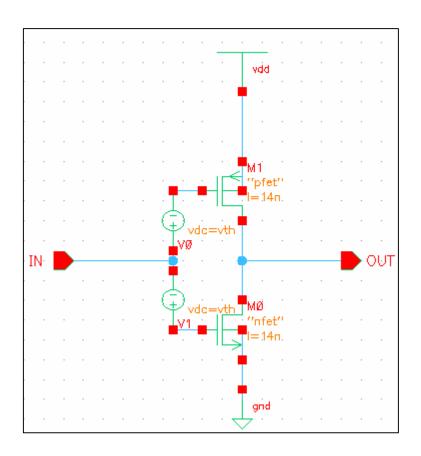

#### **3.1.2.1.** Inverter

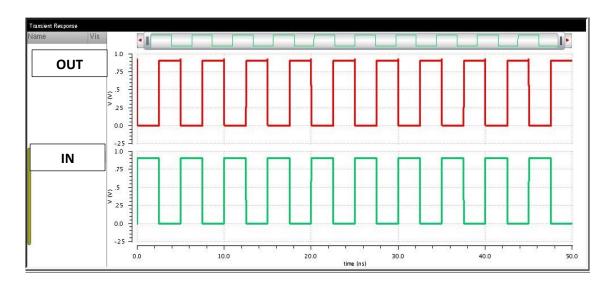

The schematic for the inverter used throughout the entire cluster design is shown in Figure 3.7, followed by Figure 3.8 which shows the simulation waveform for the inverter. Table 3.2 tabulates the measurements for 20nm technology node.

| Parameter                    | Value |

|------------------------------|-------|

| LUT size (K)                 | 4     |

| Cluster size (N)             | 3     |

| Number of cluster inputs (I) | 8     |

Table 3.1: Architecture decisions for the FPGA

Figure 3.6: Sneak-path design in FPGA cluster

Figure 3.7: Inverter schematic

**Table 3.2: Inverter simulation measurements**

| Metric       | Value |

|--------------|-------|

| Power (nW)   | 14    |

| Delay (pS)   | 3     |

| PDP (ZeptoJ) | 42    |

Figure 3.8: Inverter simulation results

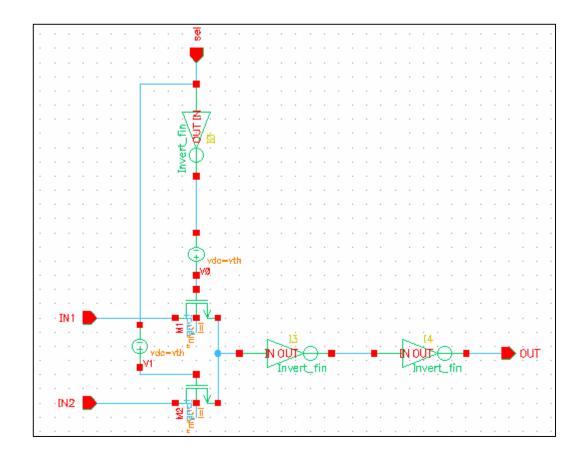

# **3.1.2.2. 2-to-1 Multiplexer**

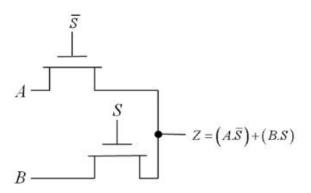

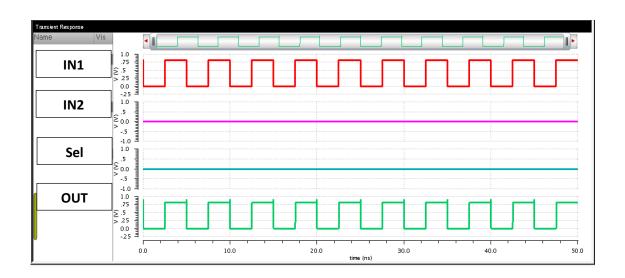

The schematic for the 2-to-1 Multiplexer used in the cluster's BLEs is shown in Figure 3.9, followed by Figure 3.10 which shows the simulation waveform where "Sel" is the selection line. The output represents selecting the first input based on the zero value for the selection line. Table 3.3 tabulates the measurements for 20nm technology node.

Figure 3.9: 2-to-1 MUX schematic

**Table 3.3: 2-to-1 simulation measurements**

| Metric      | Value |

|-------------|-------|

| Power (nW)  | 117   |

| Delay (pS)  | 19    |

| PDP (AttoJ) | 2.22  |

Figure 3.10: 2-to-1 MUX simulation results

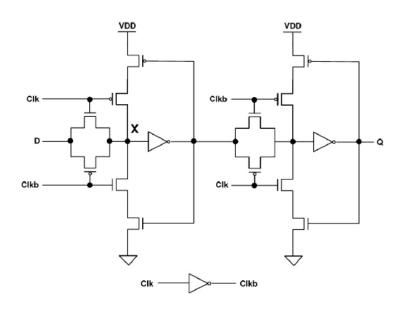

# 3.1.2.3. Transmission Gate Flip Flop (TG-FF)

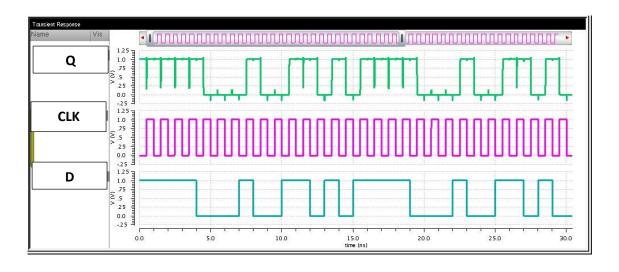

Flip-Flops and latches are used as elements for data storage; they are mandatory units for sequential logic circuits. Flip-Flop is an essential part of PLDs, FPGAs, and System on Chip (SoC) and they can be used for synchronization purposes. The schematic for the TG-FF used in the cluster's BLEs is shown in Figure 3.11, followed by Figure 3.12 which shows the simulation waveform where Q is the TG-FF output and D is the input. Table 3.4 tabulates the simulation measurements for 20nm technology node. Setup time is defined as the minimum amount of time before the clock's active edge during which data must be stable to be latched correctly. For the hold time, it's the minimum amount of time after the clock's active edge during which data must be stable.

Figure 3.11: Transmission Gate Flip-Flop schematic

Figure 3.12: TG-FF simulation results

**Table 3.4: TG-FF simulation measurements**

| Metric          | Value |

|-----------------|-------|

| Power (nW)      | 546   |

| Delay (pS)      | 13.9  |

| PDP (AttoJ)     | 7.6   |

| Setup time (pS) | 3     |

| Hold time (pS)  | 0     |

#### 3.1.2.4. SRAM

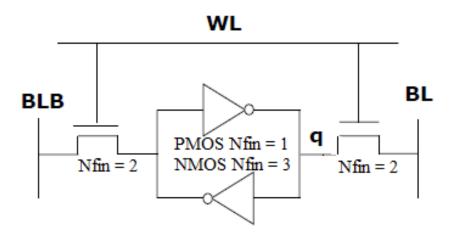

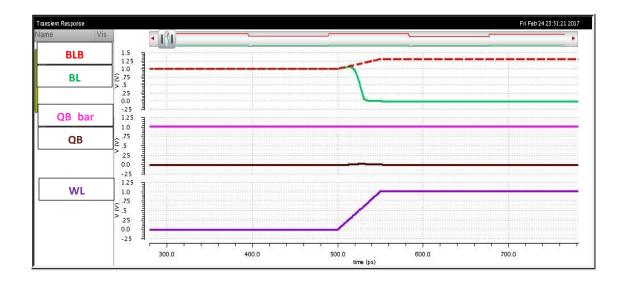

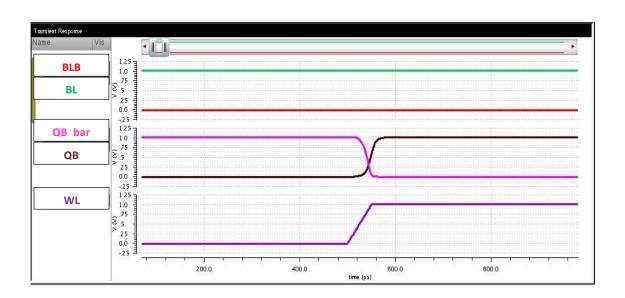

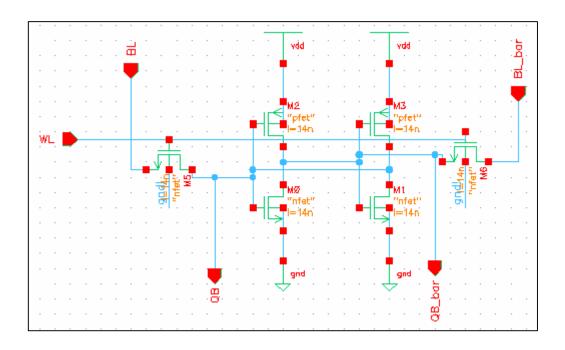

SRAM occupies a significant portion of all SoC and microprocessors as an efficient embedded memory block. In our cluster, SRAM units comprise the Lookup Table which is used to implement logic functions. The schematic for the SRAM bit cell with its sizing Figure 3.13. Figure 3.14 shows the simulation for the read operation where the bit lines (BL and BLB) are pre-charged to logic high, WL (Write Line) signal is turned on, QB is low and QB\_bar is high representing the stored values and, in turn, one of the two bit lines (BL) is going to be pulled down by the cell. Figure 3.15 shows the simulation for the write operation where we are driving one of the bit lines to high (BL) and the other one to low (BLB), and then turning on the WL signal. Bit lines will then overpower the cell with the new value (QB to logic high and QB\_bar to logic low). Table 3.5 lists the average power and write/read delay for the SRAM bit cell for 20nm technology node.

Figure 3.13: SRAM structure and sizing

Figure 3.14: SRAM simulation results (read operation)

Figure 3.15: SRAM simulation results (write operation)

**Table 3.5: SRAM simulation measurements**

| Metric           | Value |

|------------------|-------|

| Power (nW)       | 636.8 |

| Write delay (pS) | 17.42 |

| Read delay (pS)  | 33.96 |

## 3.1.2.5. FPGA 4-bit Lookup Table (LUT)

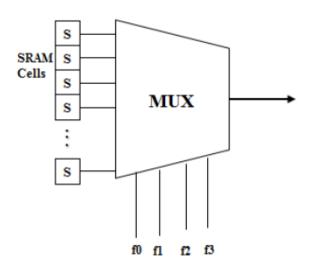

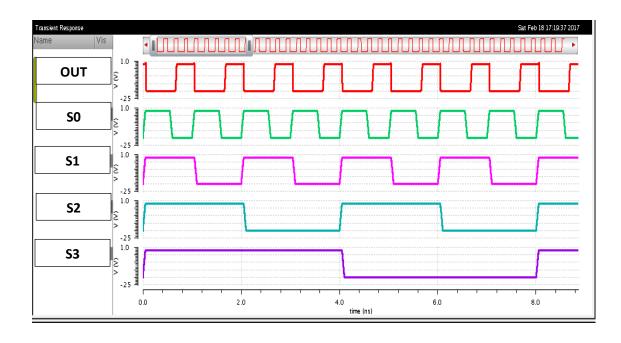

Figure 3.16 shows the overall schematic of the 4-bit LUT used to build the FPGA cluster, it consists of 16 SRAM bit cell and one 16-to-1 MUX. Simulation waveforms are shown at Figure 3.17 where from S0 to S3 represents the 4 bit selection lines for the 16-to-1 MUX to select a specific SRAM cell output. SRAM cells are programmed in the sequence of ones and zeros (101010....). Table 3.6 tabulates the measurements for 20nm technology node.

Figure 3.16: Lookup table with 4 inputs and 16 SRAM cells

Figure 3.17: Lookup table simulation results

**Table 3.6: Lookup Table simulation measurements**

| Metric      | Value |

|-------------|-------|

| Power (uW)  | 2.7   |

| Delay (pS)  | 65    |

| PDP (AttoJ) | 175.5 |

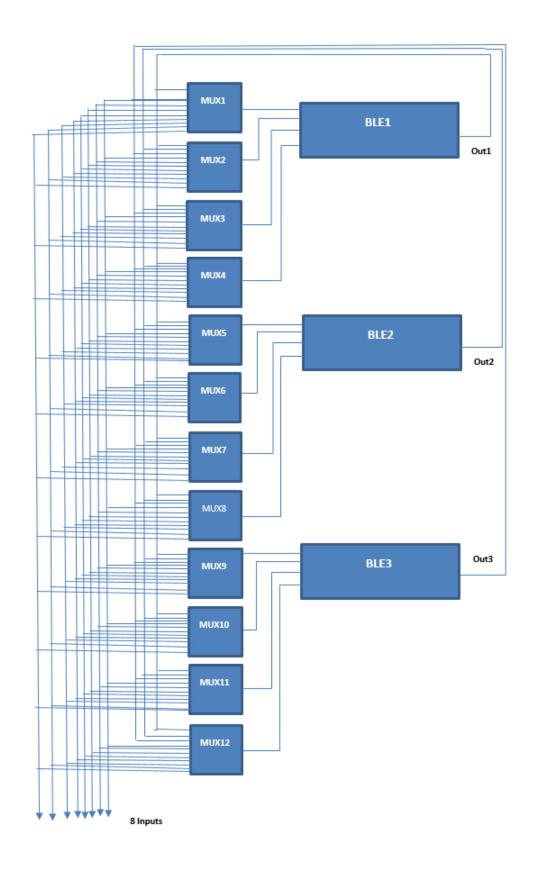

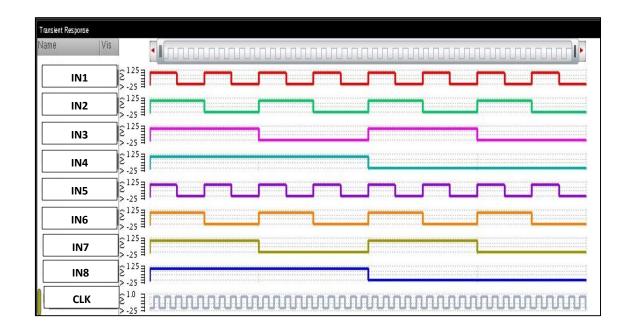

#### 3.1.2.6. FPGA Cluster

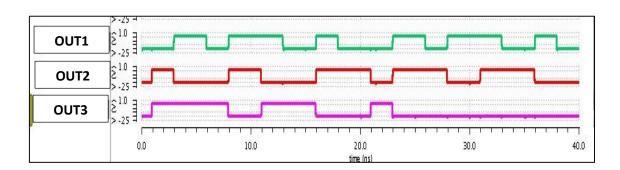

Figure 3.18 shows the overall schematic of the cluster we built for our research work including three BLEs and 12 16-to-1 multiplexer units. The FPGA cluster built for this work has been configured to build 2-bit adder benchmark circuit by manually programming the SRAM cells in LUTs accordingly and configuring the selection lines of the multiplexers to allow fully-connecting the BLEs. The 2-bit adder benchmark simulation waveforms are shown in both Figure 3.19 for the inputs and the clock signal, and Figure 3.20 for the outputs where OUT1 and OUT2 represent the sum operation, while OUT3 represents the carry output. Here we have 8 inputs representing two groups of 4 inputs, each 4 inputs group represents the two bit operation where two bits of them are added to the other two bits. So basically we have a BLE for the addition operation by the first 4 inputs group, another BLE for the addition operation by the second 4 inputs group, and the third BLE used for the carry operation, utilizing all the 3 BLEs we have in our cluster. For example, if we have the first 4 inputs group of IN1, IN2, IN3, and IN4. Here we add IN1 to IN3 and the results is OUT1, IN2 to IN4 and the result is OUT2, and the carry is in OUT3. Table 3.7 tabulates the measurements for the 2-bit adder benchmark for 20nm technology node.

Figure 3.18: FinFET-based FPGA cluster with 3 BLEs and 12 16-to-1 multiplexers

Figure 3.19: CLB inputs

Figure 3.20: CLB outputs

**Table 3.7: Cluster 2-bit adder simulation measurements**

| Metric     | Value  |  |

|------------|--------|--|

| Power (uW) | 6.49   |  |

| Delay (nS) | 0.7019 |  |

| PDP (fJ)   | 4.56   |  |

# Chapter 4: Performance Evaluation of FinFET-Based FPGA Cluster Under V<sub>th</sub> Variation

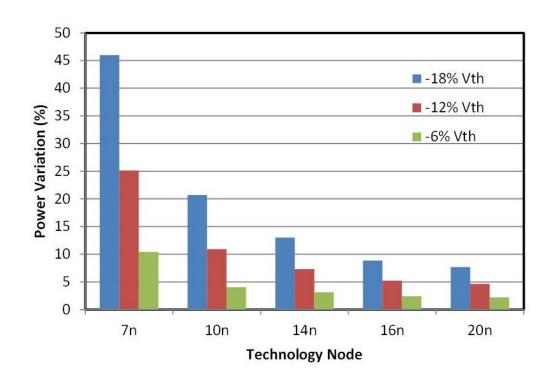

The performance of FinFET-based FPGA cluster is evaluated with technology scaling for channel length from 20nm down to 7nm showing the scaling trends of basic performance metrics. The impacts of threshold voltage variation representing D2D variations, along with the temperature variation, on the delay, power, and power-delay product are reported after simulating 2-bit adder benchmark. Simulation results show an increasing trend of the average power and power-delay product variations with threshold voltage as we go down with technology node. On the other hand, the delay shows the least percentage of variations with threshold voltage at the most advanced node of 7nm.

This chapter is organized as follows: section 4.1 gives detailed introduction about FinFETs and their dominance in the production for future technology nodes. Section 4.2 presents the simulation methodology used to measure the performance metrics. Section 4.3 presents the results and discussions of the performance evaluation study. Some design insights are given at Section 4.4. Finally, the conclusion is presented at Section 4.5.

#### 4.1. Introduction

Rigorous scaling of planar MOSFETs towards deep sub-micron regime has delivered ever-increasing transistor density and performance to ICs. However, the continuation of MOSFETs scaling in nanometer technologies is becoming extremely challenging because of the dramatic increase in the sub-threshold leakage current [7, 26, 51]. With deeply scaled MOSFETs the channel lengths are becoming very narrow and, as a result, the drain voltage starts to dominate the electrostatics of the channel and, accordingly, the gate starts to lose sufficient control over the channel. Consequently, the gate is unable to completely shut off the channel while operating in the off-mode, which increases I<sub>OFF</sub> between the source and the drain. Using highk dielectric materials and thinner gate oxides helps alleviating this problem by increasing the gate-channel capacitance. However, thinning the gate oxides is limited by the deterioration in Gate-Induced Drain Leakage (GIDL) and gate leakage [52-54]. Multiple-Gate Field-Effect Transistors (MGFETs), which are an alternative to planar MOSFETs, show better screening of the drain potential from the channel because of the proximity of the additional gate(s) to the channel (which means higher gate-channel capacitance) [5, 55-59]. This makes MGFETs superior to planar MOSFETs in shortchannel performance metrics, such as threshold voltage (Vth) roll-off, DIBL, and subthreshold slope (S). Improvement in these performance metrics implies less degradation in the transistor's V<sub>th</sub> with continued technology scaling, which then implies less degradation in I<sub>OFF</sub>.

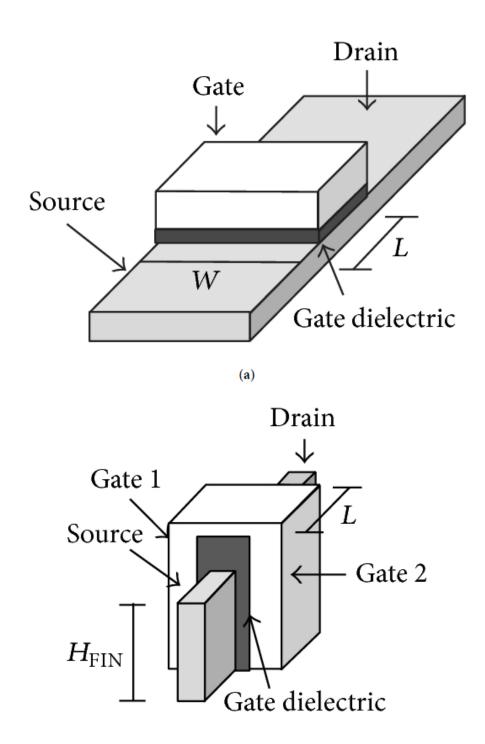

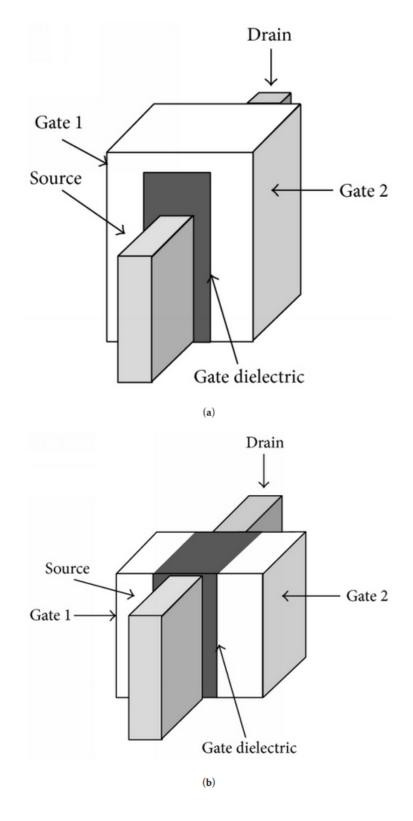

Among all MGFETs, FinFETs (as a type of DGFET) and Trigate FETs (another popular MGFETs with three gates) have emerged as the most desirable and attractive alternatives to planar MOSFETs due to their simple structure and ease of fabrication [60-68]. Figure 4.1 shows a conventional planar MOSFET and a FinFET. Two or three gates wrapped around a vertical channel (Fin) enable manageable alignment of gates and compatibility with the standard CMOS fabrication process. In Trigate FETs, an

Figure 4.1: Structural comparison between (a) planar MOSFET and (b) FinFET

additional optional etching step of the hard mask is involved in order to create the third gate on top of the channel. This third gate leads to some advantages like additional transistor width and reduced fringe capacitances despite adding to process complexity [69-71].

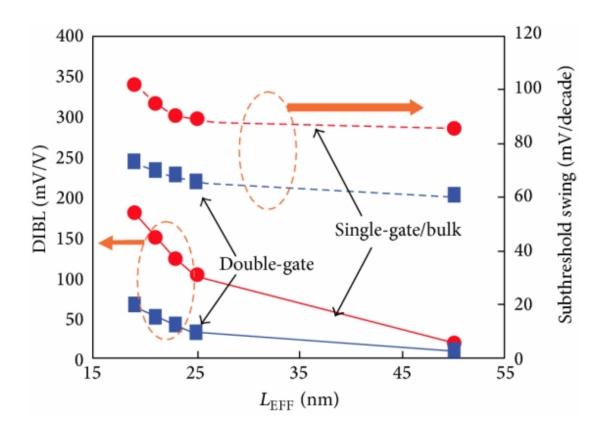

Over the past decade, FinFETs have attracted increasing attention because of the degrading short-channel behavior of planar MOSFETs [60-65]. Figure 4.2 demonstrates the superior short-channel performance of FinFETs over planar MOSFETs with the same channel length. While the planar MOSFET channel is horizontal, the FinFET channel (Fin) is vertical. Hence, the channel height ( $H_{\rm fin}$ ) determines the FinFET width (W). This leads to a special property of FinFETs known as width quantization. This property says that the FinFET width must be a multiple of  $H_{\rm fin}$ , that is, widths can be increased by using multiple fins. Thus, arbitrary FinFET widths are not possible. Although smaller fin heights offer more flexibility, they lead to multiple fins which, as a result, leads to more silicon area. On the contrary, taller fins lead to less silicon footprint, but they may also result in structural instability. Typically, the height of the fin is determined by the process engineers and is generally kept below four times the fin thickness [72, 73].

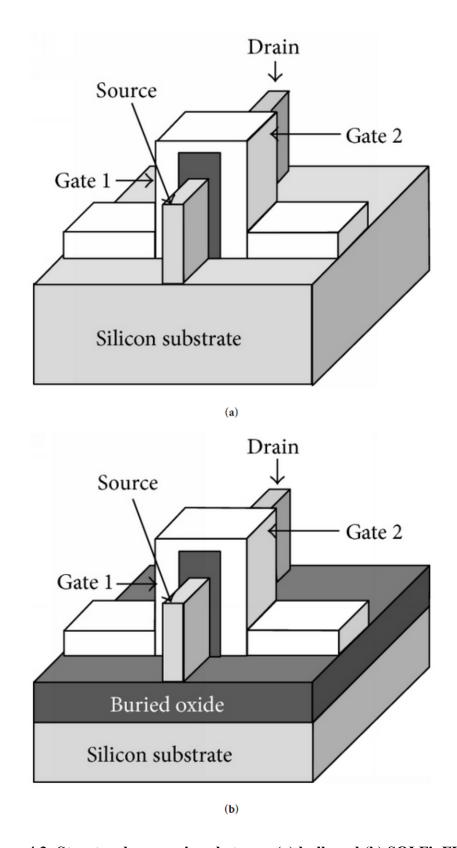

Although FinFETs implemented on SOI wafers are very popular, FinFETs have been also extensively implemented on conventional bulk wafers [74-76]. Figure 4.3 shows FinFETs implemented on bulk and SOI wafers. Unlike bulk FinFETs where all the fins share a common Si substrate/bulk, fins in SOI FinFETs are physically isolated. Some foundries prefer the bulk technology because it is much easier to migrate to bulk FinFETs from the conventional bulk MOSFETs. However, FinFETs on both types of wafers are quite comparable in terms of yield, performance, and cost. The rest of the discussion will be limited to SOI FinFETs.

Figure 4.2: DIBL and sub-threshold swing (S) versus effective channel length for double-gate (DG) and bulk-silicon nFETs. The DG device is designed with an undoped body and a near-mid-gap gate material [59]

Figure 4.3: Structural comparison between (a) bulk and (b) SOI FinFETs

Figure 4.4: Structural comparison between (a) FinFET and (b) Trigate FET

Intel firstly introduced Trigate FETs, or interchangeably referred to as FinFETs, at the 22 nm node in the Ivy-Bridge processor in 2012 [69, 77]. Figure 4.4 shows a Trigate FET along with a FinFET. The thickness of the dielectric on top of the fin is reduced in Trigate FETs in order to create the third gate. Due to the existence of the third gate, fin thickness adds to the channel width as well. Thus, Trigate FETs have a slight width advantage over FinFETs. Trigate FETs also have less gate-to-source capacitance compared to FinFETs due to additional current conduction at the top surface, but this advantage is diminished by increased parasitic resistance [70].

## 4.1.1. FinFET Classification

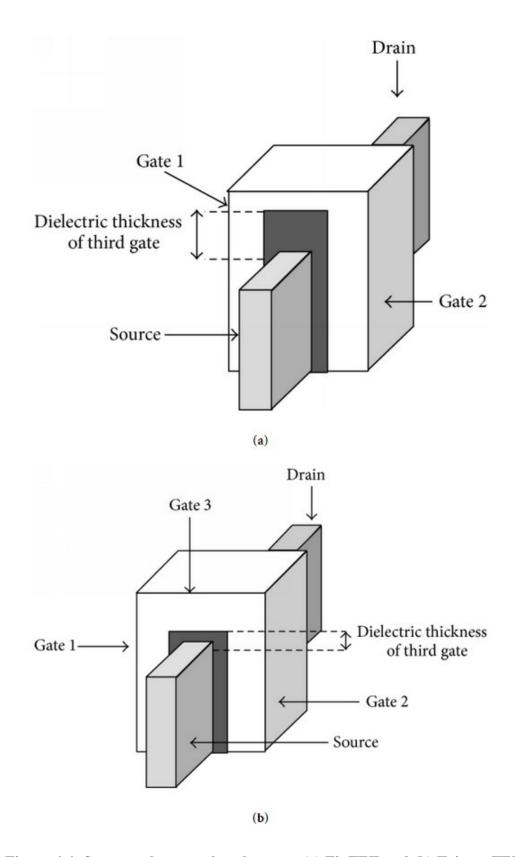

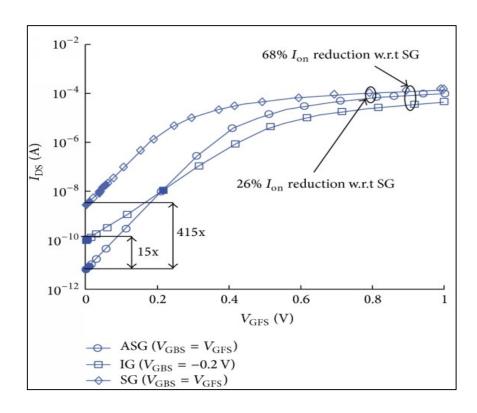

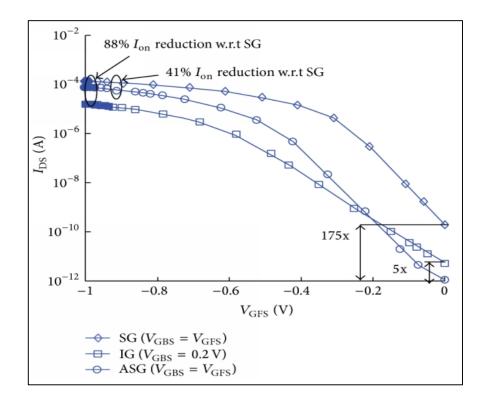

There are two main types of FinFETs: Shorted-Gate (SG) and Independent-Gate (IG). SG FinFETs are also known as three-terminal FinFETs and IG FinFETs as four-terminal FinFETs. In SG FinFETs, both the front and back gates are physically shorted, while in IG FinFETs, the gates are physically isolated (Figure 4.5). Thus, in SG FinFETs, both gates are jointly used to control the channel electrostatics. Hence, SG FinFETs show higher on-current (I<sub>ON</sub>) and also higher off-current (I<sub>OFF</sub> or the sub-threshold current) compared to IG FinFETs. On the other hand, IG FinFETs offer the flexibility of applying different voltages to their two gates. This enables using the backgate bias to linearly modulate the V<sub>th</sub> of the front gate. However, IG FinFETs have larger area overhead because of the need for placing two separate gate contacts.

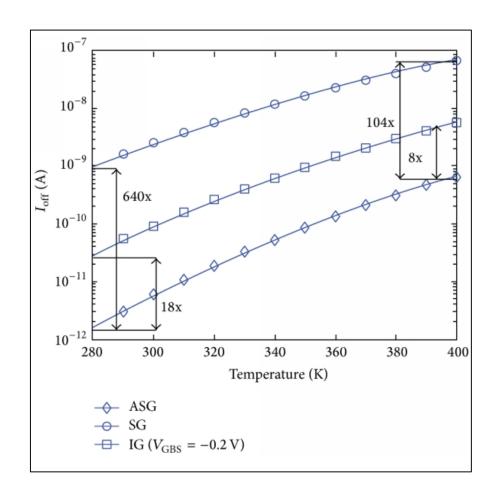

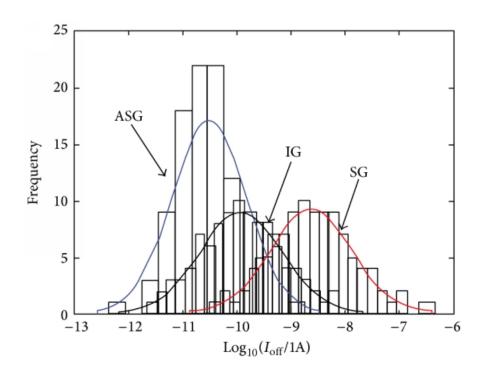

SG FinFETs can be further subdivided based on asymmetries in their device parameters. Normally, the work functions  $(\Phi_m)$  of both the front and back gates of a FinFET are the same. However, the work functions can also be made different. This leads to an asymmetric gate-work function ASG FinFET [78, 79]. ASG FinFETs have very promising short-channel characteristics with  $I_{OFF}$  that is two orders of magnitude lower than that of an SG FinFET, with only somewhat lower  $I_{ON}$  than that of an SG FinFET [80]. They can be fabricated with selective doping of the two gate-stacks. Figures 4.6 and 4.7 show comparisons of the drain current versus front-gate voltage curves for SG, IG, and ASG nFinFETs and pFinFETs, respectively, demonstrating the advantages of ASG FinFETs.

Figure 4.5: Structural comparison between (a) SG and (b) IG FinFET

Figure 4.6: Drain current (IDS) versus front-gate voltage (VGFS) for three nFinFETs [80]

Figure 4.7: Drain current (IDS) versus front-gate voltage (VGFS) for three pFinFETs [80]

## 4.1.2. Process Variations for FinFET

In order to tackle the Sort-Channel Effects (SCEs) in planar MOSFETs, a sufficient number of dopants must be injected into the channel. However, this means that RDF may lead to a significant variation in  $V_{th}$ . For instance, at deeply scaled technology nodes, the  $3(\sigma/\mu)$  variation  $V_{th}$  in caused by discrete impurity fluctuations can be greater than 100% [81]. Since FinFETs enable better SCEs performance due to the existence of a second gate, they do not need a high channel doping to ensure a high  $V_{th}$ . Hence, designers can keep the thin channel (fin) at nearly intrinsic levels ( $10^{15}$  cm<sup>-13</sup>). This, in turn, reduces the statistical impact of RDF on  $V_{th}$ . The desired  $V_{th}$  is obtained by engineering the gate work function instead. Low channel doping also ensures better mobility of the carriers inside the channel. Thus, FinFETs emerge superior to planar MOSFETs by alleviating a major source of process variation.

Due to their small dimensions, along with the lithographic limitations, FinFETs do suffer from other process variations and they are subjected to many important physical fluctuations, such as variations in gate length ( $L_{GF}$ ,  $L_{GB}$ ), gate-oxide thickness ( $T_{OXF}$ ,  $T_{OXB}$ ), fin-thickness ( $T_{SI}$ ), and gate underlap ( $L_{UN}$ ) [81–87]. For example, gate oxide is

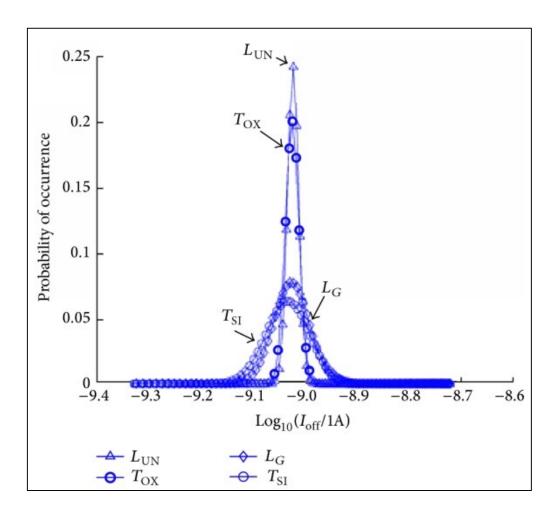

Figure 4.8: Distribution of leakage current (Ioff) for different process parameters, each varying independently [84]

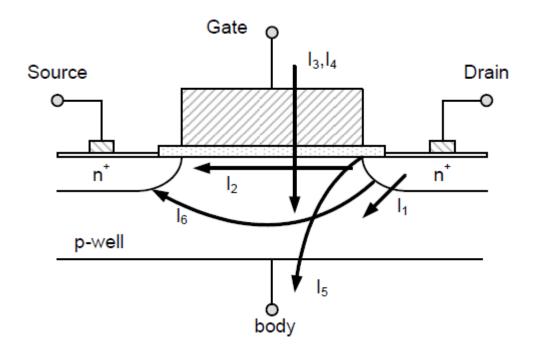

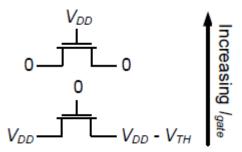

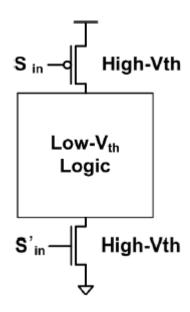

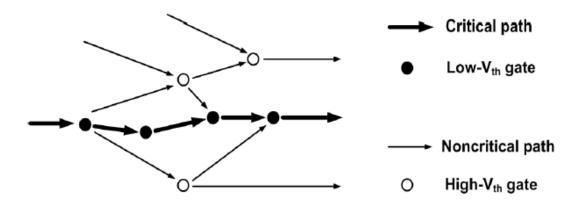

on the etched sidewall of the fin, and may suffer from non-uniformity. The degree of non-uniformity depends on the fin's Line-Edge Roughness (LER) fin. LER also causes variations in fin thickness. Figure 4.8 illustrates the impact of parametric variations on the sub-threshold current (I<sub>OFF</sub>) of an nFinFET.